# DEVELOPMENT OF A REAL-TIME VISION SYSTEM FOR AN AUTONOMOUS MODEL AIRPLANE

Danko Antolovic

Submitted to the faculty of the University Graduate School in partial fulfillment of the requirements for the degree

Master of Science in the Department of Computer Science Indiana University

October, 2001

| Accepted by the Graduate Faculty, Indiana University, in partial fulfillment of the |                                |  |

|-------------------------------------------------------------------------------------|--------------------------------|--|

| requirements for the degree of Master of Science.                                   |                                |  |

|                                                                                     |                                |  |

|                                                                                     |                                |  |

|                                                                                     |                                |  |

|                                                                                     |                                |  |

|                                                                                     | Prof. Steven D. Johnson, Ph.D. |  |

|                                                                                     |                                |  |

|                                                                                     |                                |  |

| Thesis committee                                                                    | Prof. Florin Cutzu, Ph.D.      |  |

|                                                                                     |                                |  |

|                                                                                     |                                |  |

|                                                                                     | Prof. Michael E. Gasser, Ph.D. |  |

|                                                                                     |                                |  |

|                                                                                     |                                |  |

| September 21, 2001.                                                                 |                                |  |

Copyright © 2001

Danko Antolovic

ALL RIGHTS RESERVED

#### **ACKNOWLEDGMENTS**

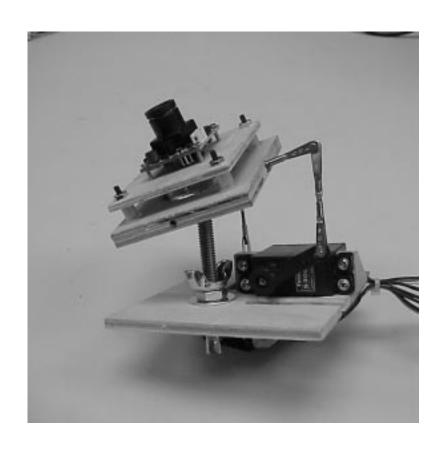

This thesis is a description of a hardware/software system constructed in a series of Y790 independent study courses in the Department of Computer Science at Indiana University. The work was done under the supervision of Professor Steven D. Johnson, to whom I am grateful for his support, his interest in the progress of the project, and for his insightful and critical comments. Professor Johnson constructed the camera gimbal currently in use.

I am happy to have had the help of Mr. Bryce Himebaugh, engineer and pilot extraordinaire. Beside constructing the A/D converter and the servo circuit, Bryce has shared his knowledge and skill through many helpful and enjoyable discussions.

I also wish to thank Professor Robert DeVoe of the IU School of Optometry. His expertise on animal vision has helped me establish a broader context for some of the problems encountered in robotic perception.

Finally, my thanks go to Laurie, my spouse, for her patience during this, the latest of my academic stints.

#### **ABSTRACT**

#### Danko Antolovic

# DEVELOPMENT OF A REAL-TIME VISION SYSTEM FOR AN AUTONOMOUS MODEL AIRPLANE

This thesis describes a real-time embedded vision system capable of tracking two-dimensional objects in a relatively simple (uncluttered) scene, in live video. This vision system is intended as a component of a robotic flight system, used to keep a model airplane in a holding pattern above an object on the ground. The system uses a two-pronged approach to object tracking, taking into account the motion of the scene and the graphic "signature" of the object. The vision system consists of these main components: a motion-detection and filtering ASIC, implemented on FPGAs, a scene-analysis program running on a Motorola ColdFire processor, a dual-port RAM holding the image data, and a digital camera on a motorized gimbal.

## **CONTENTS**

|                 |                   |                                           | Page |

|-----------------|-------------------|-------------------------------------------|------|

| Acknowledgments |                   | iv                                        |      |

| Abs             | tract             |                                           | V    |

| 1.              | Intro             | duction to the Skeyeball Vision Project   | 1    |

|                 | 1.1               | History of the vision system              | 1    |

|                 | 1.2               | Structure of this document                | 4    |

| 2.              | Func              | Functional Overview of the Vision System  |      |

|                 | 2.1               | Vision methodology                        | 8    |

|                 | 2.2               | Biological parallels                      | 11   |

| 3.              | 3. Project Status |                                           | 13   |

|                 | 3.1               | Capabilities and limitations              | 13   |

|                 | 3.2               | Measurements of the tracking speed        | 13   |

|                 | 3.3               | Summary remarks on the perception problem | 16   |

| 4.              | Hard              | ware Architecture                         | 19   |

|                 | 4.1               | Architectural components                  | 19   |

|                 | 4.2               | Biomorphic approach to architecture       | 20   |

| 5.              | Desig             | gn Summary                                | 24   |

|                 | 5.1               | XC4010 digital design                     | 24   |

|                 |                   | 5.1.1 Front-end FPGA                      | 24   |

|                 |                   | 5.1.2 Back-end FPGA                       | 25   |

|                 | 5.2               | MCF5307 (ColdFire) code                   | 26   |

| 6.  | NTSO   | C Video Signal                             | 28 |

|-----|--------|--------------------------------------------|----|

|     | 6.1    | Even field                                 | 28 |

|     | 6.2    | Odd field                                  | 31 |

| 7.  | Form   | atting the Image Scan                      | 33 |

|     | 7.1    | Vertical formatting                        | 34 |

|     | 7.2    | Horizontal formatting                      | 37 |

|     | 7.3    | Auxiliary components                       | 39 |

|     | 7.4    | Signals                                    | 40 |

| 8.  | Digiti | izing and Thresholding                     | 42 |

|     | 8.1    | Black-and-white inversion                  | 42 |

| 9.  | Settin | ng the Threshold Automatically             | 43 |

|     | 9.1    | Heuristic procedure                        | 43 |

|     | 9.2    | Threshold calculation on the back-end FPGA | 45 |

|     |        | 9.2.1 Data path                            | 45 |

|     |        | 9.2.2 Control                              | 47 |

|     |        | 9.2.3 Signals                              | 47 |

| 10. | Digita | al Zoom                                    | 51 |

|     | 10.1   | Zoom implementation on the FPGA            | 52 |

| 11. | Roun   | d Robin Procedure for Data Sharing         | 55 |

|     | 11.1   | Status byte                                | 57 |

|     | 11.2   | Round robin on the front-end FPGA          | 59 |

|     | 11.3   | Round robin on the MCF5307 processor       | 63 |

| 12. | Pixel  | read/write cycle                           | 64 |

| 13. | Frame   | e Comparison and the Motion Vector       | 68 |

|-----|---------|------------------------------------------|----|

|     | 13.1    | Methodology                              | 68 |

|     | 13.2    | Computation                              | 69 |

|     | 13.3    | Design components                        | 69 |

|     | 13.4    | Signals                                  | 70 |

| 14. | Writin  | ng the Motion Vector to DPRAM            | 72 |

| 15. | Paran   | neters of the Front-End FPGA             | 75 |

| 16. | IRQ5    | IRQ5/Parallel Port Complex               |    |

|     | 16.1    | IRQ5 handler                             | 80 |

|     | 16.2    | Duty-cycle generator                     | 81 |

|     | 16.3    | Servo motion feedback                    | 81 |

|     | 16.4    | Displacement vector                      | 81 |

|     | 16.5    | Saccadic blanking                        | 82 |

|     | 16.6    | IRQ/PP circuit on the back-end FPGA      | 83 |

| 17. | Auxil   | Auxiliary Features                       |    |

|     | 17.1    | Serial communication with the MCF5307    | 88 |

|     | 17.2    | Diagnostic data logging                  | 88 |

|     | 17.3    | Soft restart of the vision program       | 88 |

|     | 17.4    | Radio controls                           | 89 |

|     |         | 17.4.1 Radio decoder's signals           | 90 |

| 18. | Featu   | re Recognition on the MCF5307 Processor  | 91 |

|     | 18.1    | Main data structures in the MCF5307 code | 93 |

| 19. | Initial | lization of the SBC5307 Board            | 95 |

| 20.        | Characteristics of the Camera/Servo System | 96  |

|------------|--------------------------------------------|-----|

| 21.        | Supplementary Diagrams                     | 98  |

| References |                                            | 101 |

#### 1. INTRODUCTION TO THE SKEYEBALL VISION PROJECT

Skeyeball is an ongoing project in the Department of Computer Science at Indiana University. It is centered around a radio-controlled model airplane, which is being converted into a semi-autonomous vehicle. Its primary perception is a computer vision system, and it will also be equipped with attitude sensors, digital video and telemetry downlink, and digital command uplink.

The objective is to give the airplane the autonomy to fly beyond the line of sight, navigate, and find objects of interest by their visual appearance rather than by location.

The objective of the work described here was to build a vision system that follows an object in a relatively simple (uncluttered) scene, in live video. This vision system will be integrated into a larger robotic navigation system used to steer the airplane into holding pattern above a selected feature on the ground.

## 1.1 History of the vision system

The Skeyeball vision was first envisioned as a subsystem implemented on a microcontroller chip. Soon it became obvious that a fast (and not too costly) implementation of the early processing stages was needed: vision became an ASIC-cummicroprocessor system, and it is still such a system today.

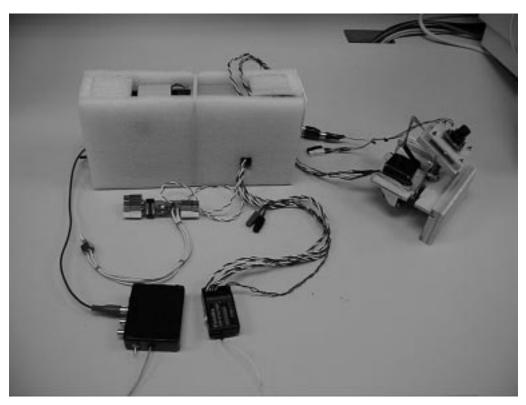

Picture 1: Aerial view of a target overflight

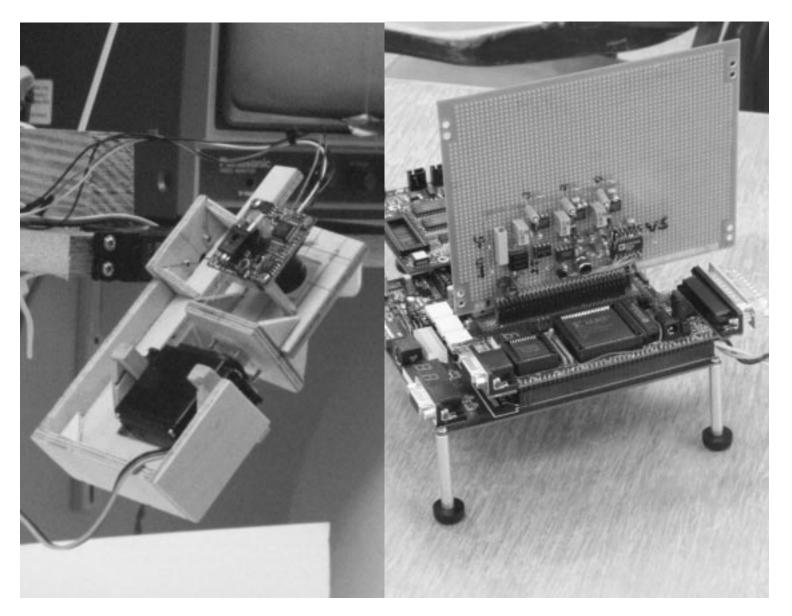

The development has gone through two distinct phases. The first phase yielded a strictly laboratory prototype: the hardware was built from proto boards, and the processors were a Xilinx XC4010 FPGA and a Motorola MC68332. Data were shared through an SRAM on the common bus. This architecture required considerable data copying, and the 25 MHz MC68332 processor was rather too slow for the task. Nevertheless, the system was capable of (slow) object tracking, moving a camera on a simple gimbal. Pictures 2 and 3 show the gimbal and the circuitry of the first phase.

We then obtained some realistic footage by flying the airplane with the immobile camera. The laboratory prototype was capable of detecting target features in overflight sequences, but tracking an object reliably at flight speeds was very problematic. Picture 1 shows a

typical aerial view: the plane casts its shadow next to the bright square target (a brightly colored blanket on the grass).

This first phase gave us a fairly good insight into the minimal requirements of such a system. The second (current) phase is described in the rest of the thesis. Two major architectural improvements are a faster microprocessor (90 MHz Motorola ColdFire) and a dual-port RAM for shared data. Elimination of one very cumbersome proto board has also made the ASIC (application-specific integrated circuit) implementation much easier.

The fundamental vision algorithm has not seen much change over time, except for the addition of the threshold calculation in the second phase - the improvement has been the increased speed. Much greater modifications had to be made to the data flow procedures, to take advantage of the dual-port memory and better bus architecture.

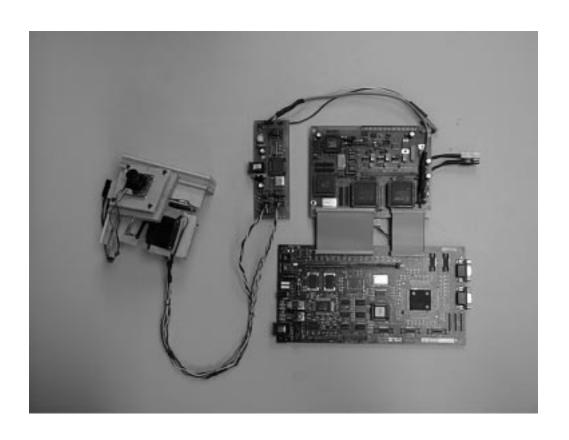

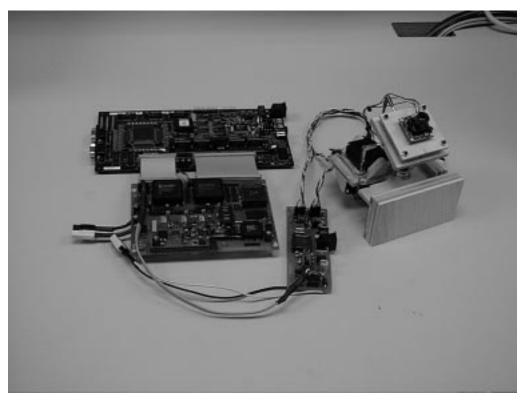

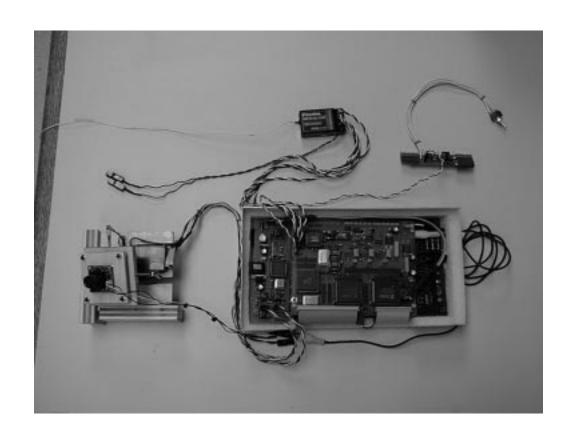

Finally, in the second phase, the system was given the proper startup procedure and radio controls, and the entire circuitry was built so as to be suitable for mounting inside the airplane. Pictures 4-7 show the equipment built in the second phase: three circuit boards, the new camera gimbal and the radio-controlled power switch. Picture 7 also shows the radio and TV links connected to the vision system.

#### 1.2 Structure of this document

This document serves a dual purpose: it describes the constructed system as a solution to an engineering/computational problem in broad terms; it also describes it at the level of detail needed for modification and further development.

The system divides itself naturally into several subsystems. The first five sections of this document provide an overview, and the remaining sections describe the subsystems separately, with the level of detail increasing within each subsystem description. We have tried to make it clear where the broad description ends and the detailed one begins: typically, detailed descriptions are grouped into specialized subsections.

The ultimate level of detail - schematics, pinout lists and the source code - has been relegated to electronic form. This document contains summary descriptions of those materials, as well as passages referring directly to source details. Interested reader should become familiar with the circuit schematics and the source code.

Picture 2: Gimbal, phase 1

Picture 3: Circuit boards, phase 1

Pictures 4,5: Circuit boards and gimbal, phase 2

Pictures 6,7: Vision system, radio and TV links, power switch

#### 2. FUNCTIONAL OVERVIEW OF THE VISION SYSTEM

## 2.1 Vision methodology

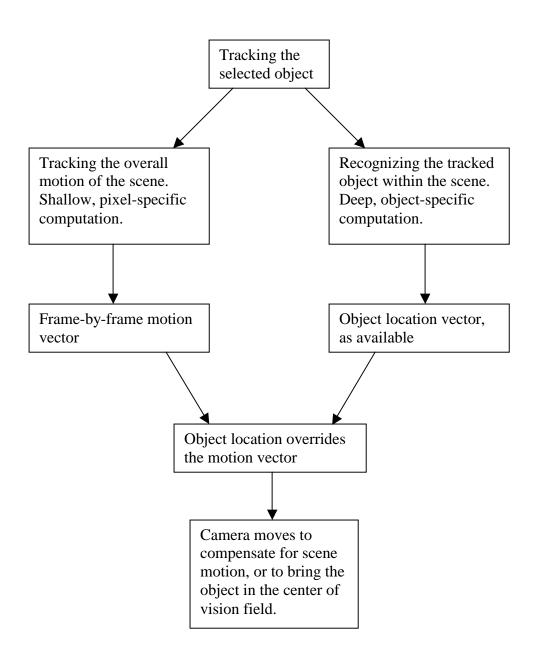

As we stated in the introduction, the objective of this work was to build a vision system that will follow an object in a relatively simple scene, in live video. We have used a two-pronged approach to object tracking, taking into account the motion of the scene and the graphic "signature" of the object.

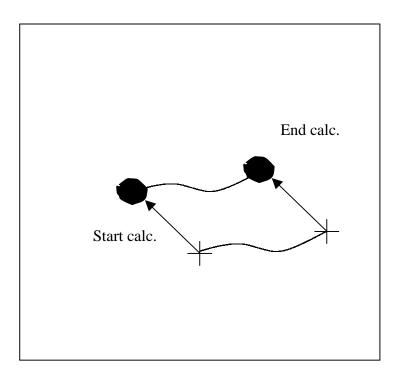

This approach was motivated by the fact that object recognition is computationally intensive, and impossible to accomplish on a frame-by-frame basis with the available hardware. Nevertheless, the vision system must operate fast enough not to allow the object to drift out of the field of vision. Picture 9 illustrates this point.

The objective is to recognize the small dark object as the target, obtain its offset from the center of the vision field, and move the camera to bring the object to the center.

Obviously, the vision system must take a still frame and base its calculation on it. In the meantime, the object will change location, perhaps even drift out of the field. By the time it is calculated, the displacement vector may well be irrelevant.

To avoid this, the motion of the scene is tracked frame by frame, and the camera moves to compensate for it. The center of the field moves along with the target, and the displacement vector, when available, will still be meaningful. It should be said, however, that the importance of the drift compensation decreased as we used a much faster processor in the second phase of the project (see Section 1.1).

Picture 8: Method overview

Object recognition requires several stages by which redundant and non-essential visual information is parsed out, until we are left with a selection of well-defined objects, also referred to as the features of the scene. In our case, the stages are: thresholding, edge detection, segmentation into connected components, clean-up and signature/location calculation.

Picture 9: Drift compensation

Picture 10 gives a functional overview of the vision system, where the progressively thinner arrows signify the reduction in bulk of the visual information. This is the typical "funnel" of the vision problem, leading from simple computations on large volume of data to complex ones on a small volume, yielding a number or two as the result.\*

10

<sup>\*</sup> At 30 frames per second, 483 lines per frame, and 644 byte-sized pixels per line, raw camera output amounts to 9.33 Mbytes /sec. The 644 samples per line of continuous signal conform to the 4:3 aspect ratio prescribed by NTSC, and one byte per pixel is a realistic choice of color depth.

To identify a target object within the scene, we used the second moments about the object's principal axes of inertia as the "signature." Second moments are invariant under rotations and translations, fairly easy to calculate, and work well in simple scenes.

## 2.2 Biological parallels

It is not entirely surprising that certain functional analogies should develop between robotic perception, such as this real-time vision system, and perception in animals. While such analogies must not be taken too literally, they provide a glimpse at useful generalizations to be made about perception problems, and we will sketch them out as appropriate.

For example, camera motion based on feature recognition bears a similarity to the (involuntary) saccadic motion of the eyes, the one-shot movement that brings a detail of interest into the center of the vision field.<sup>1</sup> Eyes' saccades are fast, have large amplitude (as large as the displacement of the object of interest), and they are ballistic movements, i.e. they are not corrected along the way. Such a motion is compatible with a need for speed over precision: if the object identification is computationally intensive, use the result to full extent, and as fast as possible.

At the end of the process, the vision produces a few dozen bytes every couple of frames – actual rate depends on the contents of the image.

Picture 10: Functional overview

#### 3. PROJECT STATUS

#### 3.1 Capabilities and limitations

We have tested the lab vision system by manually moving irregular shapes in a vision field fairly free of random clutter, and also by means of a rotating table (Section 3.2 below).

The recognition system tracks its target reliably under translation and rotation, and in the presence of several shapes introduced as interference. Excessive skew breaks off the tracking, since the vision algorithm makes no provision for it, but an oblique view of ca. 20 degrees is still acceptable (Section 3.2). Likewise, occlusion is interpreted as a change of shape, and the target is lost when partially occluded (e.g. by drifting beyond the edge of the vision field). These limitations are obvious consequences of the vision methodology described in Section 2.1 and Picture 10.

The tracking and motion detection work equally well with the zoom engaged. As expected, zoom makes the system more reliable in tracking small targets, at the expense of limiting the field of vision to the central one-ninth.

## 3.2 Measurements of the tracking speed

The Skeyeball airplane flies within certain ranges of speed and altitude; our fixed-camera flights have ranged from 18 to 60 mph, with a typical speed of ca. 35 mph.

Likewise, target-overflight altitudes have been from 60 to 320 ft. Consequently, the line of sight to the target feature changes direction relative to the body of the airplane, with

certain angular velocity, and the vision system must be able to keep up with it. In the test flights, the target passed through the vision field of the fixed camera in time intervals ranging from 0.8 to 4.2 seconds, depending on the altitude and velocity of the airplane.

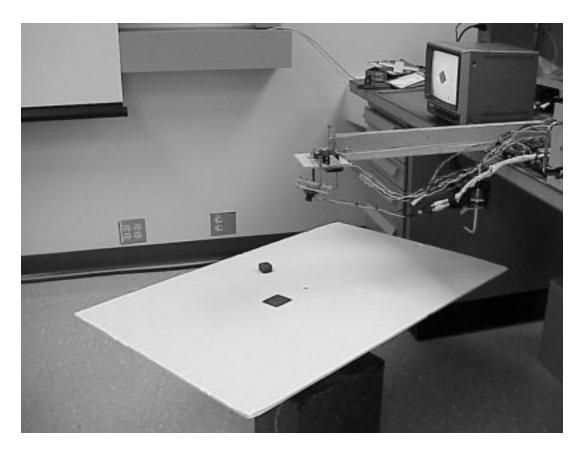

In order to obtain some quantitative measure of the vision's tracking abilities, we have constructed a test rig - a rotating table with features to track. The vision system locks successfully onto the (largest) presented feature and the camera turns following the rotation of the table. The rotation speed is gradually increased, until the tracking breaks off or target acquisition becomes impossible. Picture 11 shows the experimental setup: the camera gimbal, the rotating table with two features, and the TV screen showing the camera's view.

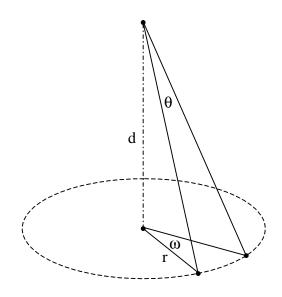

Picture 12 shows the geometry of the setup. The speed of the table's motor was regulated by applying variable voltage, and the angular speed of the table was measured as the time needed for ten turns. A simple formula relates the table's angular speed  $\omega$  to the camera's sweeping speed,  $\theta$ :

$$\theta = \frac{\omega}{\sqrt{1 + \left(\frac{d}{r}\right)^2}}$$

Picture 11: Laboratory set-up for the tracking-speed measurements

Picture 12: Table speed vs. the camera's sweep

d is the elevation of the camera above the table, and r is the distance of the target feature from the center of the table.

At d = 26.5 cm, and r = 10 cm, we found that the tracking was still reliable with the camera sweeping an arc at the maximum speed of:

$\theta(\text{max}) = 45 \text{ degrees/second.}$

The camera's field of vision is ca. 47 degrees high and ca. 60 degrees wide (see Section 20), which puts this vision system within the range of speeds required to keep up with the overflight speeds that were quoted above.

Of course, tracking speed depends on the complexity of the scene. These measurements were performed with two or three shapes, plus an intermittently visible edge of the table. The scene observed in a real flight is richer in features, but at least for grassland and trees, features tend to have low contrast and disappear below the threshold, which in turn is set to single out high-contrast targets.

#### 3.3 Summary remarks on the perception problem

Real-time perception can be envisioned as a funnel in which the data volume is reduced, but the algorithmic complexity increases. Typically, there will be several stages with fairly different breadth/depth ratio.

This is intrinsically not a problem amenable to single-architecture processing. Of course, a speed tradeoff is in principle always possible, but engineering considerations such as

power consumption and heat dissipation place a very real limit on that approach. We believe that it is better to use several processor architectures, each suitable for a different stage of the perception process. Appearance on the scene of configurable microchips makes this goal both realistic and appealing.

Robotic perception is also a problem in embedded computing. Requirements imposed by the small model airplane are a bit on the stringent side, and one can envision a much more relaxed design for an assembly line or security system. However, the need for perception is naturally the greatest in mobile robots. In such applications the vision system will always have to be compact and autonomous, because it bestows autonomy on a mobile device whose primary function is something other than carrying a vision system around.

Architecture should follow function, starting at a fairly low level. For example, data collection in this system is done with a digital camera which serializes the (initially) parallel image input. This choice was dictated by good practical reasons, but the system lost a great deal of processing power because of that serialization. Image input should have been done in parallel, which in turn would have required a specialized device and a much broader data path in the initial processing stage.

The segmentation stage is better suited for implementation on general-purpose processors because of the smaller data volume and more "sequential" algorithms. An architectural alternative may be possible here: segmentation could be attempted on a highly connected

neural net circuit, trading off an exact algorithm for an approximate, but parallelizable, search procedure. Neural net searches, on the other hand, are usually slow to converge and may not improve the overall speed.

Animal vision cannot be separated from cognitive functions and motor coordination, and this must be true for robotic vision as well. How much "intelligence" is built into high-level processing of visual information depends on the ultimate objectives of Skeyeball: for example, searching for a 3D shape in a complex panorama is a problem different from that of hovering above a prominent feature on the ground.

In terms of steering and motor coordination, biological parallels are relevant. It is known that inertial motion sensors play a large role in the gaze control of mobile animals [1]. Since the input from the motion sensors is simpler, and the processing presumably faster, this sensory pathway provides the supporting motion information much faster than can be obtained by visual processing. The airplane may very well benefit from an eventual integration of its vision and attitude/motion sensors.

Visual perception is an ill-posed problem, and examples of functioning compromises may be more valuable than exact results. Throughout this document, we point out similarities with biological systems which strike us as interesting, although we do not pursue them in depth for lack of expertise on the subject. A few pitfalls notwithstanding, we believe that a synthesis of computational, physiological and engineering knowledge will be necessary for the eventual development of reliable and versatile perception systems.

## 4. HARDWARE ARCHITECTURE

## 4.1 Architectural components

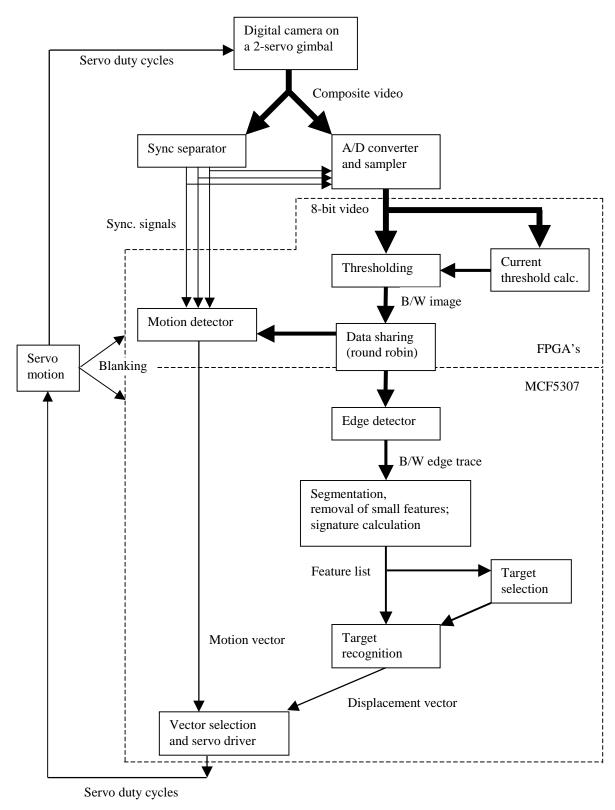

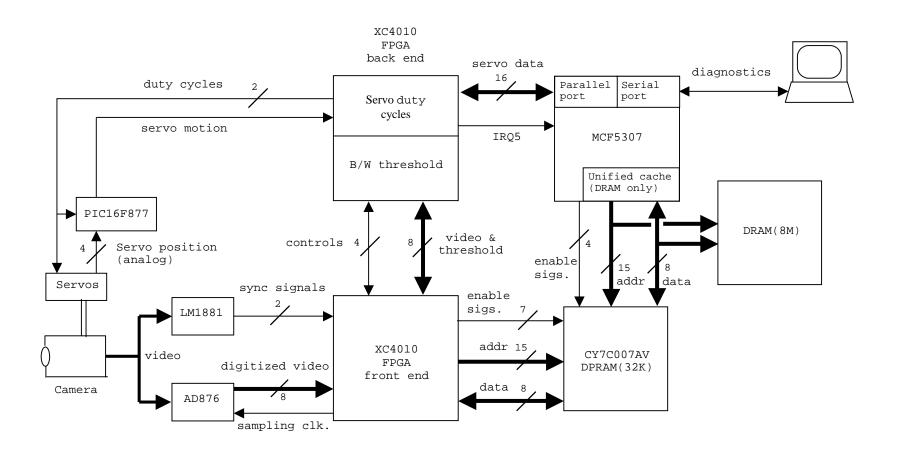

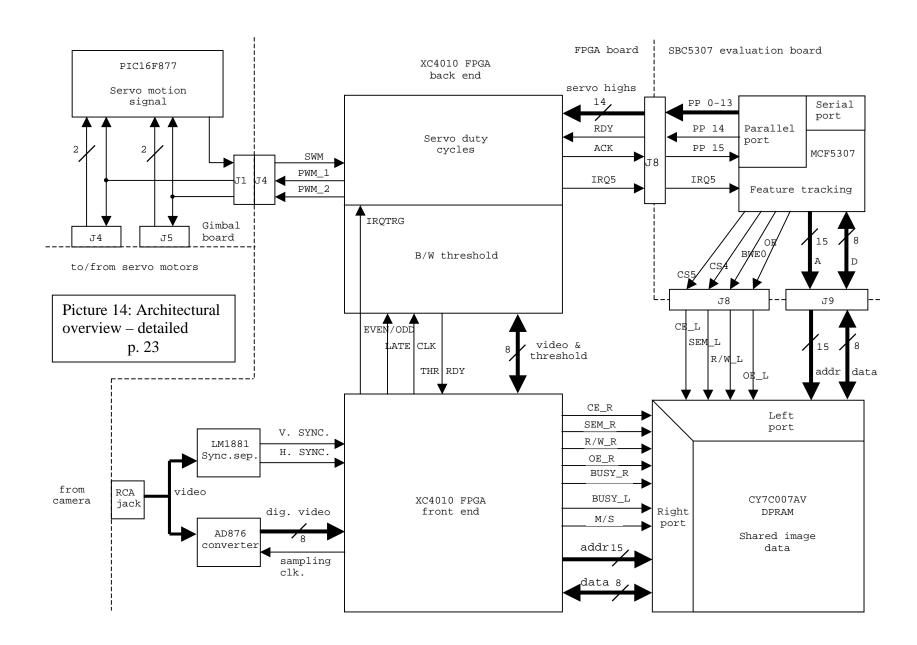

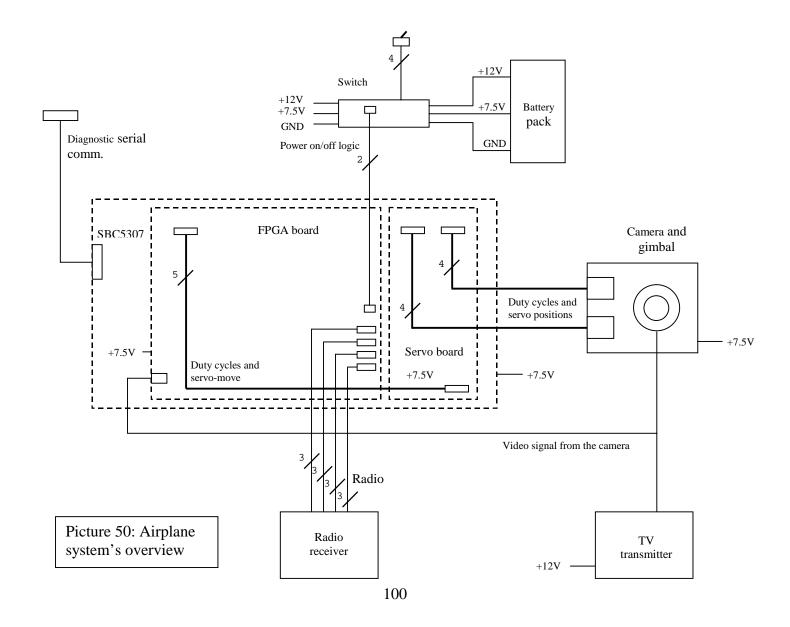

Picture 13 is an overview of the architecture of the vision system. Picture 14 shows all the signals pertaining to the flow of data from the camera, through the processors and back to servo motors, but it omits some peripheral details.

Camera - The "eye" of the system is a small digital camera, producing grayscale (non-color) NTSC video signal; its other characteristics are largely unknown. The camera is mounted on a gimbal driven by two servo motors, with a 50-degree range of motion in each direction, and is permanently focused on infinity.

Sync separator – the NTSC grayscale video signal contains three synchronization signals.

These are extracted by means of video sync separator LM1881 by National

Semiconductor, mounted on a prototyping board along with supporting circuitry.

A/D converter – we use Analog Devices' AD876, which is a pipelined 10-bit converter. It is mounted on the same proto board, with supporting circuitry for its reference voltages.

Sampling control, thresholding and threshold calculation, motion detection and zoom are implemented as digital designs on a synchronous pair of Xilinx XC4010 FPGA's, running at 33.3 MHz. Start-up configuration is done with two Atmel's AT17LV config ROMs.

The entire object recognition is implemented as code, running on a 90 MHz Motorola MCF5307 ColdFire integrated microprocessor. We use a commercial evaluation board, SBC5307, with 8 megabytes of DRAM, start-up flash ROM, expansion bus and communication ports.

The two processors share image data through a 32K dual-port SRAM, CY7C007AV by Cypress Semiconductor. Data access is implemented as a round-robin procedure, with the objective of speeding up high-volume data transfer in the early stages of the vision process.

The driver for the servo motors that move the camera is implemented on one of the two FPGA's. Motion feedback from the servos is generated by a PIC16F877 microprocessor, on the basis of servos' analog position signals.

## 4.2 Biomorphic approach to architecture

Nervous systems of animals utilize specialized hardware almost by definition. There is much evidence that biological architecture follows function: for example, the retina, with its layers of many specialized types of cells, is apparently a structure which has evolved to deal with the initial stages of the vision funnel, from the cellular level up.

Architecture of this robotic system follows the same "biomorphic" principle as much as possible. In order to increase overall speed and throughput, we have opted for ASICs and dedicated data paths, even at the cost of under-utilizing some components. Multitasking

and time-multiplexing are systematically avoided. Biological systems follow this principle because of evolutionary constraints, but they solve the real-time perception problem well, and the trade-offs they make appear to be the right ones.

Picture 13: Architectural overview

#### 5. **DESIGN SUMMARY**

This section provides a top-level summary of the schematics and code modules which comprise the functional configuration of the hardware described in Section 4.

## 5.1 XC4010 digital design

Configuration of the two FPGA processors is implemented with the Xilinx Foundation development tool, either as schematics or as Abel HDL code.<sup>2</sup> This list gives an overview of the functionalities contained in the highest-level modules. Design components and signals are described throughout the text and in the schematics themselves.

#### 5.1.1 Front-end FPGA

This design consists of seven top-level schematics and a number of macros. It utilizes about 60% of the logical blocks (CLBs) of the XC4010 FPGA.

VISION\_IN – contains the entry point for the video sync signals, vertical and horizontal image framing and sampling, and the zoom.

ANALOG\_IN – input from the A/D converter, normalization to black reference level, black-and-white thresholding.

FIELD\_END – placeholder schematic, invoking macros for vector output, run-time parameters and the round robin.

VISION\_OUT – input/output to the DPRAM.

RR\_ADDRESS – address counters for image buffers, round-robin address multiplexer.

MOTION\_VECT – invokes the pixel read/write cycle, calculation of the motion vector.

CLOCKS – entry point for the external clock and reset signal, generation of internal clocks.

## 5.1.2 Back-end FPGA

The design consists of five top-level schematics and a number of macros. It utilizes 96% of the CLBs of the XC4010 FPGA.

DUTY\_CYC\_PP – IRQ5/parallel port communication, duty cycle generator, servomotion signal.

HIST\_DP – data path for the threshold search in the histogram.

HIST\_IO\_RAM – histogram storage and management.

HIST\_MINMAX – comparison logic for the threshold search, control ASM.

HIST\_INTEGRAL – calculation of the histogram and features area.

## 5.2 MCF5307 (ColdFire) code

Programs running on the MCF5307 ColdFire processor are written in C and ColdFire assembler,<sup>3</sup> and compiled/assembled with GNU "gcc" and "as." This list groups the code modules by system function; further description is provided in the text and in the source comments.

main.c - initialization and main loop for feature recognition

## Configuration and startup:

cache.s - cache initialization

ConfigRegs.s - MCF5307 configuration, running from flash

ConfigRegs2.s - MCF5307 configuration, running from DRAM

crt0.s - setup for the C language

globals.c - init. of global variables for functional code

glue.c - heap setup and other book-keeping

start.s - processor startup sequence

vector.s - vector table

## Feature recognition:

ConnectedComponents.c - segmentation algorithm

Diagnostics.c - vision system's error reporting

FeatureDetector.c - feature "signatures"

FeaturePoints.c - maintenance of heap data structures

Features.c - driver modules for acquisition and tracking

GraphDFS.c - depth-first graph traversal

SimpleEdge.c - edge detector

## Inter-process communication:

CyclesPP.s - communication through the parallel port

IRQHandler.s - handler for the Interrupt 5 (Process 1)

roundRobin.s - round-robin DPRAM access

## Servo motion:

servo.s - translating displacements to servo duty cycles

## Auxiliary:

Datalog.c - interface library for the diagnostic data log

DataOutput.c - diagnostic data output

serial.c - communication library for the serial port(s)

SerialHandler.s - UART interrupt handler

IRQ7Handler.s - handler for the Interrupt 7 (soft restart)

TermInput.c - stub for the terminal command input

#### 6. NTSC AND THE EVENTS SYNCHRONOUS WITH THE VIDEO SIGNAL

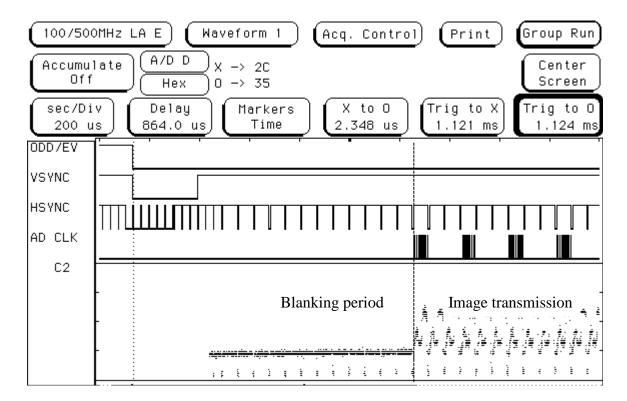

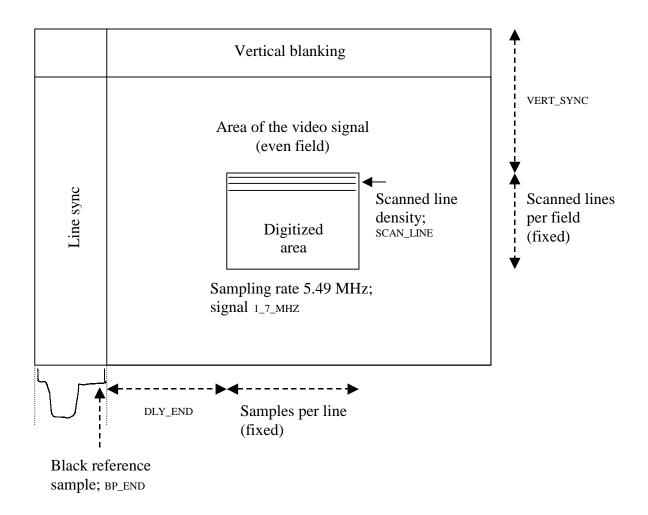

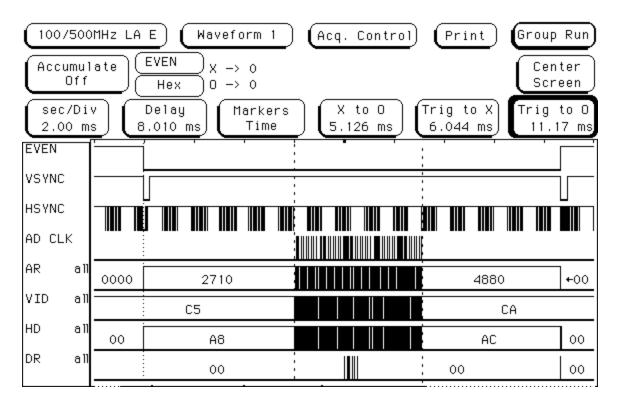

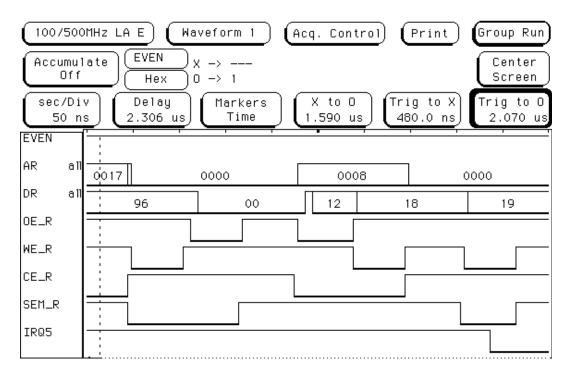

Frames of the NTSC television signal<sup>4</sup> consist of two interleaved fields, marked by an even/odd synchronization signal. At the beginning of each field there is a period of time when the beam retraces back to the top of the image (at low intensity), a period marked by the vertical synchronization signal. Also, horizontal retracing between video lines is marked by the horizontal sync.<sup>5</sup> Pictures 15 to 18 show some details of the operations synchronous with the video signal.<sup>†</sup>

We sample the content of the video signal during the even field of each frame, and at variable resolution – every third line in the absence of zooming, every line when the zoom is engaged. Motion detection, which compares adjacent video frames, is performed simultaneously with the sampling, between the pixels, as it were. An early fraction of the odd field is used for communication between processes and for the threshold calculation.

#### 6.1 Even field

Picture 15 shows the beginning of the even field, the synchronization signals, the A/D sampling clock, and the composite analog video signal. Notice the long vertical blanking period before the beginning of the actual image transmission.

† Pictures 15-18, 27, 28, 32, 35, 38 and 42 are screen shots from a Hewlett-Packard 16500B logic analyzer.

28

Picture 15: The even field

The sampling clock operates in bursts, during the sampled portion of the even field (see Pictures 15, 16, 19 and 26). First sample of each line is taken during the so-called back porch of the horizontal sync, at the black reference intensity. We use the first sample as the zero reference for the remaining grayscale values in that line: there is quite a bit of intensity wobble in the camera signal, and this referencing makes the image steadier.

Picture 16 shows the video content of one line, the sampling clock and the thresholded digital data obtained from the video signal. The values of one (black pixels) in the middle of the line correspond to the dip in the video signal, which was in turn caused by a dark object at the top of camera's vision field.

Picture 16: Video signal carrying one line

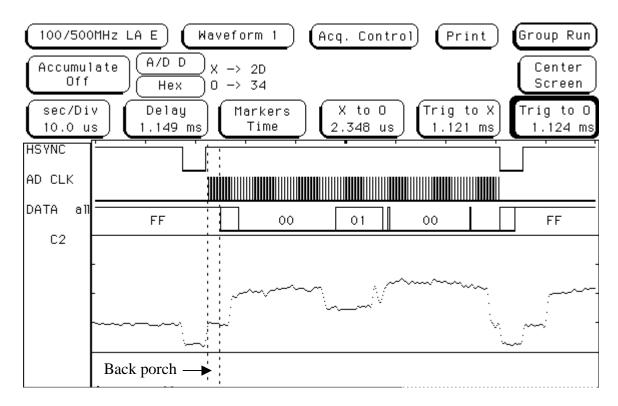

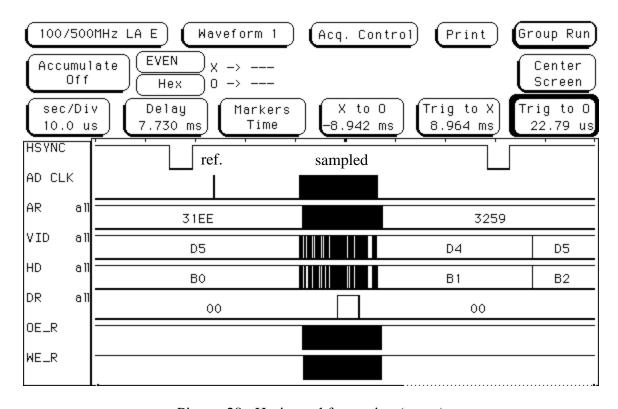

Picture 17, at 1.7 MHz sampling rate, shows the delay between the sampling clock and the return of digital data. The A/D converter is pipelined,<sup>6</sup> introducing a delay of four clock periods, which we account for by delaying the beginning of pixel read/write cycles. The I/O at the end of the line extends past the sampling clock by the same amount.

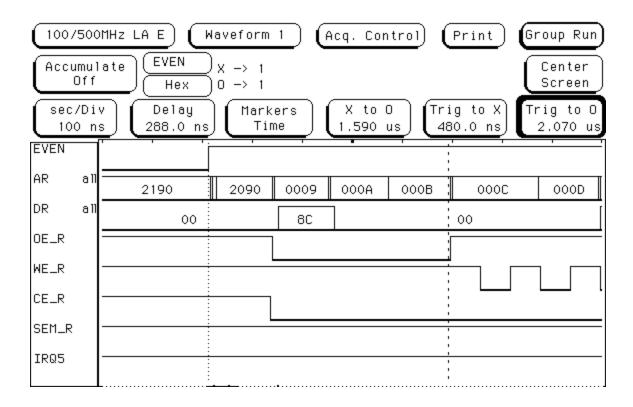

The field AR is the pixel's address in the DPRAM (right port), VID is the converter's output. First tick of the AD clock occurs at the end of back porch, and the resulting black reference value is latched four ticks later, as 0x31 in the VID signal. HD is the normalized grayscale value: notice that VID – HD = 0x31 past the black reference.

DR is the thresholded signal, showing in this case a black object in the first line. OE\_R, WE\_R and CE\_R are the memory control signals of the DPRAMs right port.

Picture 17: A/D pipeline delay

Motion vector calculations and storage of the digital image are described in Section 12, dealing with the pixel read/write cycle (p. 64).

## 6.2 Odd field

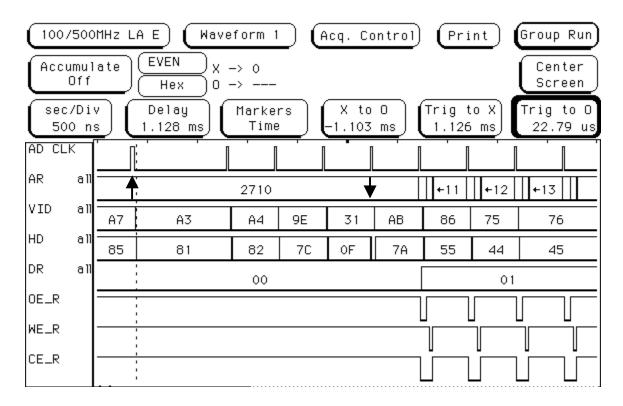

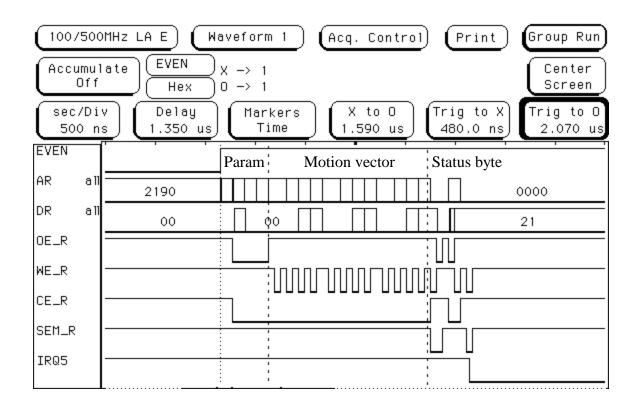

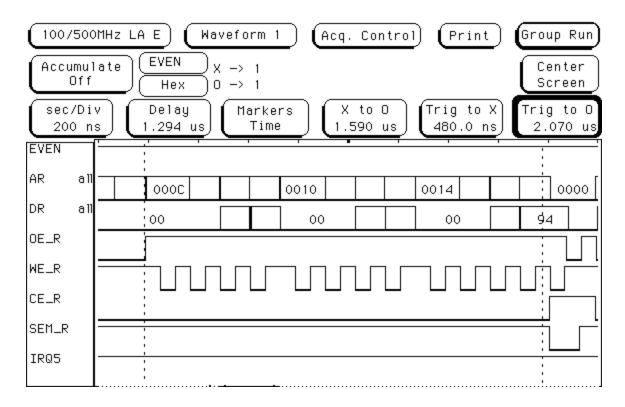

Picture 18 shows the beginning of the odd field and the DPRAM I/O associated with it.

At this time, parameters are updated, the motion vector has been calculated and is written

out (notice the twelve dips in the WE signal), and Process 1 updates the status byte (notice that the semaphore operation SEM\_R brackets the status byte read and write). IRQ5 is asserted, triggering the handler on MCF5307 and starting the parallel-port communication (see Section 16, on IRQ/PP).

Picture 18: The odd field

## 7. FORMATTING THE IMAGE SCAN

The design receives the sync signals already separated from the total video signal. It uses the syncs to control the digitization and framing, to assign coordinates to pixels, and to count total numbers of pixels and black pixels in the image. For convenience in analyzing the VCR video signal, which does not have the even/odd sync, this sync signal is being generated internally.

Deciding at which points to sample the video signal, i.e. generating a sampling clock for the A/D converter, is the main functionality derived from the synchronization signals. Vertical formatting means the selection of video lines, while the horizontal formatting means a selection of discrete sampling points on the continuous video signal. The two formats differ in details, and are made somewhat more complex by the presence of the zoom (see Section 10, on the digital zoom). Also, in this system, sampling is limited to the even field of the frame.

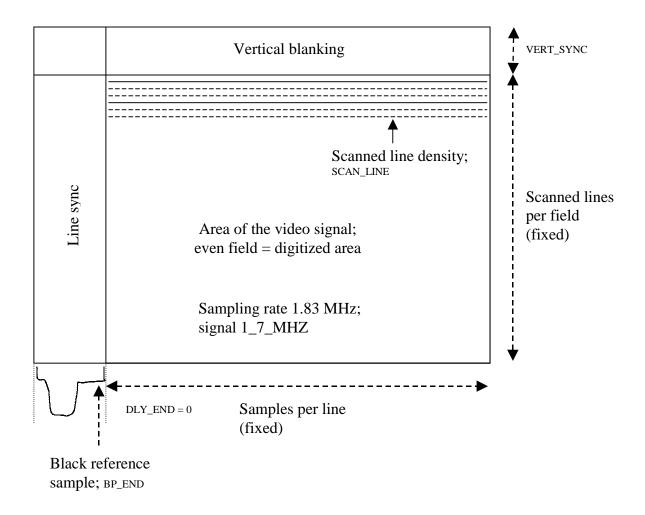

Picture 19 shows the formatting geometry and the signals involved, in the absence of zooming. Zoom geometry is shown in Picture 26.

Picture 19: Formatting and sampling

# 7.1 Vertical formatting

Briefly, the vertical formatting circuit (in the schematic VISION\_IN) determines three things:

- at which line in the even field to start sampling

- at what line density to scan (how many lines to skip between scans, if any)

- how many lines to scan (i.e. when to stop)

# 7.1.1 Starting line

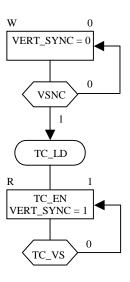

Obviously, sampling must be suppressed during the vertical retrace (vertical blanking), and when the 3X zoom is engaged, over the top third of the image as well. This is accomplished by extending the duration of the vertical sync to the first scanned line, counting the requisite number of lines. A loadable counter and a small ASM, triggered by the signal VSNC and clocked by LINE\_SYNC, produce the signal VERT\_SYNC, which extends to the first scanned line.

Picture 20: VERT\_SYNC ASM

## 7.1.2 Line density

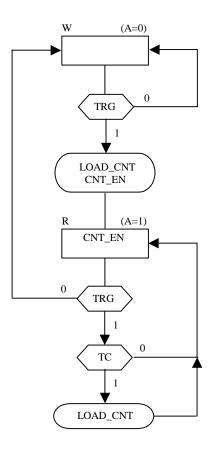

Component LOAD\_CNT2 is a counter which reloads an external value D\_IN whenever it runs out, then continues running to that value. It has a provision for the zero count, and two term count signals, full period and half period. It runs while its TRG input is high. This component is used to set the line density, by clocking it with LINE\_SYNC.

Picture 21: LOAD\_CNT2 ASM

#### 7.1.3 Line count

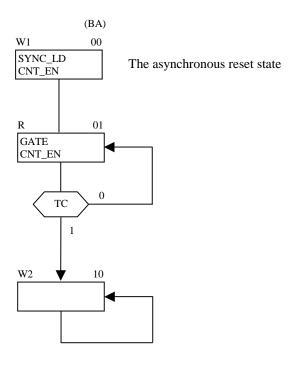

Component SCAN\_LPF is a stopping counter which is reset asynchronously on the rising edge of its TRG input. Its output GATE remains high for the duration of the count; afterwards the counter sleeps until the next reset. This component is used to count the scanned lines in the even field.

Picture 22: SCAN\_LPF ASM

# 7.2 Horizontal formatting

The horizontal formatting circuit (also in VISION\_IN) does these four things:

- decides at what pixel density to sample

- produces the sampling signal for the black reference at a fixed position in line

- decides where in the scanned line to start sampling pixels

- and how many pixels to sample per line (i.e. when to stop)

# 7.2.1 Pixel density

An ASM and a loadable counter, identical to those in LOAD\_CNT2, generate a clock signal at the pixel sampling frequency, by reducing the system clock by a factor dependent on the zoom.

### 7.2.2 Black reference sampling

Component LOAD\_CNS is a counter which synchronously loads an external value D\_IN, runs to that value and stops. It has a provision for the zero count, and two term count signals, full period and half period. It starts when its SYNC\_LOAD input goes high.

This component is used to generate the black ref. sampling signal (BPE), by counting off the length of the back porch in the intervals of the sampling clock.

# 7.2.3 Starting pixel

A second LOAD\_CNS counts off the delay from BPE to the first pixel (zero, or one third of the line for the 3X zoom). It raises the signal EN\_SAMP, during which pixel sampling is enabled.

#### 7.2.4 Pixel count

An ordinary counter counts the sampled pixels in the line, and lowers the EN\_SAMP when the full number of pixels is reached.

# 7.3 Auxiliary components

CLK\_DELAY – this component creates bursts of its input clock CLK, for the duration of the input CTRL, only delayed by a fixed number of clock periods. CLK is assumed to be a continuous clock. This component is used to create a clock burst delayed by four clock periods, which is needed to latch the output from the A/D converter's pipeline.

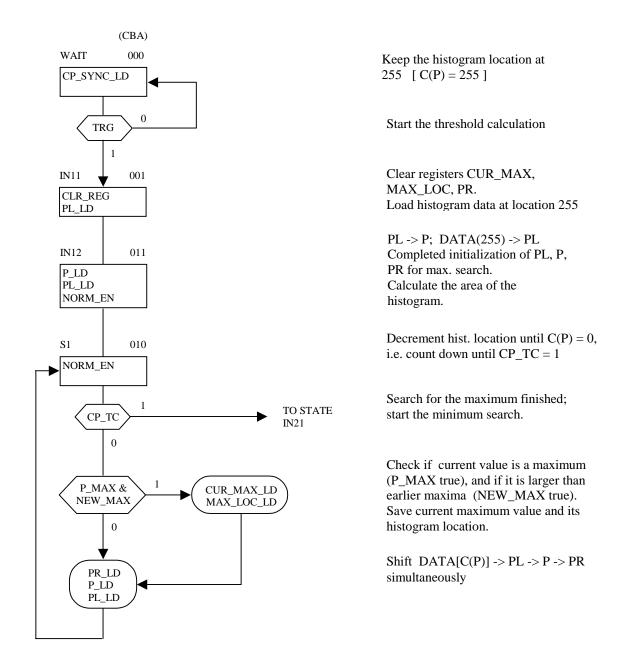

HCP (half-clock pulse) – passes to Q the first high half-period of CLK, following the rising edge of its input D, and only that. It is used to convert the term-count signals (which last a full clock period) into half-period pulses. The component is asynchronous, and uses three FF's (A,B and C) which mutually clear each other, according to this timing diagram:

•.•.• signifies a flip-flop in continuous clear

Picture 23: HCP timing diagram

# 7.4 Signals

Sync signals are active low, inverted and used as active high through the design. In order to process still-frame output from VCRs, which lacks the odd/even signal, this signal is generated internally.

LINE\_SYNC - active high delimiter between video lines, typically 4.7 microseconds. Suppressed during the odd field.

VSNC - active high delimiter between fields, typically 230 microseconds. Suppressed during the odd field.

VERT\_SYNC - derivative of VSNC. Extends from the beginning of VSNC to the first sampled line in the field, covering vertical retrace and vertical zooming delay. Covers up unused synchronization interval in LINE\_SYNC.

SCAN\_LINE – active high during each scanned line; reflects the vertical sampling density (every line or every third line, set by the zoom level). Its derivative SCAN\_L1 is low during horizontal syncs. Both signals are active only during even fields.

EN\_SAMP - when this signal is high, pixel sampling of the video line is permitted. This signal is high in every n-th video line, as set by SCAN\_LINE, and covers either the entire line or the middle third of it, as set by the zoom level.

1\_7\_MHZ - clock which controls the density of pixel sampling of the video lines. At 108 pixels per line, this clock runs at 1.83 MHz or 5.49 MHz, depending on the zoom level (see clock-reducing counter).

BP\_END - the single pulse indicating the end of back porch. Its delayed derivative, LATE\_BPE, is used to latch the black reference level. Unlike the rest of the sampling signals, these are not affected by the zoom.

AD\_CLK - triggering signal sent to the A/D converter. It comprises BP\_END and the 1\_7\_MHZ line sampling burst covered by EN\_SAMP.

LATE\_CLK – line sampling burst, delayed by several periods (4) of the sampling clock, to allow for pipeline delay in the A/D converter. This signal clocks the utilization of the digitized signal.

DLY\_END – single pulse indicating the end of horizontal zooming delay.

# 8. DIGITIZING AND THRESHOLDING (schematic ANALOG\_IN)

Video signal from the camera is digitized with the AD876 converter chip. The circuit generates the sampling trigger for the converter, AD\_CLK, and receives 8-bit grayscale signal, VIDEO, in return.

Video signal is corrected for the intensity fluctuations by subtracting the black reference value from it. The corrected video is thresholded to a strictly black and white signal, C\_BIT, which is both stored in the RAM and passed to frame comparators.

The corrected video is also passed to the back-end FPGA for histogram/threshold calculation, during the even field. In the odd field, the signal THR\_RDY from back-end latches the calculated threshold into a data register, to be used in the next frame.

Presently, the sampling is done on 81 lines of every even field of the video signal, at 108 pixels per line. This yields a 108x81 b/w digitized image frame, at the correct NTSC width-to-height ratio of 4:3.

#### 8.1 Black-and-white inversion

Which side of the threshold is considered active, or a feature, is a matter of convention, and can be set by a run-time parameter. The choice does not affect the edge detection, although it affects the sensitivity of the motion detector somewhat.

# 9. SETTING THE THRESHOLD AUTOMATICALLY

## 9.1 Heuristic procedure

This vision system operates on the assumption that the scene consists of relatively luminous target feature(s) and relatively dark uninteresting background (or the reverse). An early and important step is to set a black-and-white threshold that will separate the features from the background, greatly reducing the complexity of the scene.

Setting this threshold manually is a delicate task. The selection is guided by the apparent simplicity of the b/w image, and once set, the threshold usually works well for a range of similar images. It would be difficult for the navigator to adjust the threshold in flight, and small errors in the threshold can alter the result dramatically. Automatic thresholding was implemented to make the vision more robust.

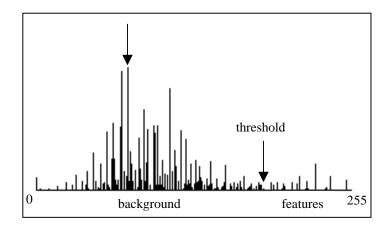

Finding the threshold follows this heuristic procedure:

- a) Construct the grayscale histogram of the image. This is a straightforward pixel count, accumulated in an array of 256 grayscale levels.

- b) Find the highest maximum in the histogram and assume that it is located in the middle of a large "hump" representing the background.

- c) Find the lowest minimum on one side of the highest maximum (in this case, the brighter side). Set the threshold to that grayscale level: the area opposite (brighter than) the background hump represents features.

- d) Disregard threshold choices which define a very small feature area in the histogram, since they typically have no visual significance.

- e) If the search for a meaningful minimum fails, reverse the grayscale and look for features on the opposite end of the histogram in the next video frame

### f) Clear the histogram.

The assumption here is that the lowest minimum gives best separation of the histogram into background and features of interest, and the success ultimately depends on the grayscale separability of the image. Picture 24 gives an illustration of the procedure.

The grayscale version of the image is not currently used in the later vision stages; neither is the value of the threshold. For that reason, the histogram/threshold process is implemented in hardware, on the back-end XC4010 connected to the front-end vision processor via a dedicated data bus. While the histogram/threshold algorithm is well suited for implementation in code, running it on the ColdFire processor would have complicated the data flow and slowed down the feature recognition.

Picture 24: Sample histogram

# 9.2 Description of the threshold calculation on the back-end FPGA

## 9.2.1 Data path

The histogram is stored in a synchronous RAM component, SYNC\_RAM, which is contained in the schematic HIST\_IO\_RAM, along with elements which build (and clear) the histogram. There are 256 word-sized locations in SYNC\_RAM; the histogram is maintained by presenting the grayscale value to the RAM as the address, and incrementing the corresponding location by one (or setting it to zero).

During the histogram build (even field), histogram addresses are the video data coming from the front-end FPGA through the bus HIST\_IO. Depending on the nature of the image, these grayscale values may be inverted by subtracting them from 255. During the threshold calculation (odd field), HIST\_ADDR is generated internally by a counter, and histogram values appear on the bus HIST\_OUT.

The threshold calculation sweeps the histogram twice, by convention in downward direction (255 to 0, white to black). The sweep of histogram addresses is generated by the counter C(P); specific count values are latched in MIN\_LOC and MAX\_LOC registers, as the locations of histogram extrema (schematic HIST\_DP).

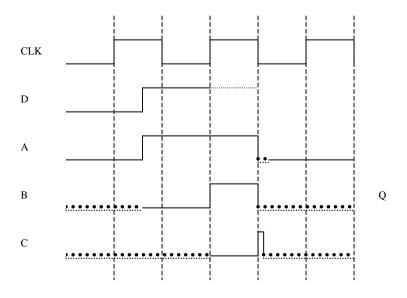

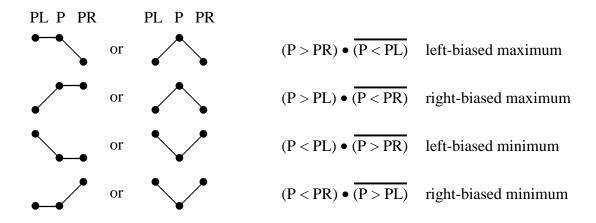

Minima and maxima are detected by comparing three adjacent histogram values, which flow through the comparison registers PL, P and PR during the sweep. These are the relevant comparisons, with black dots representing relative heights of the adjacent bars of the histogram:

We use the left-biased comparisons. Current extremes are latched into registers CUR\_MIN and CUR\_MAX. Since we are interested in the global extremes, locally found extremal values must be compared with current largest/smallest values. All the comparison logic is contained in the schematic HIST\_MINMAX.

Step d) from previous section is implemented in the schematic HIST\_INTEGRAL.

Histogram integral and the features integral are accumulated in registered adders, and the features integral is compared with an appropriate fraction of the total histogram integral.

Since the search for a meaningful minimum can fail, the success/failure is recorded in the flip-flop MIN\_FOUND and passed to the control ASM.

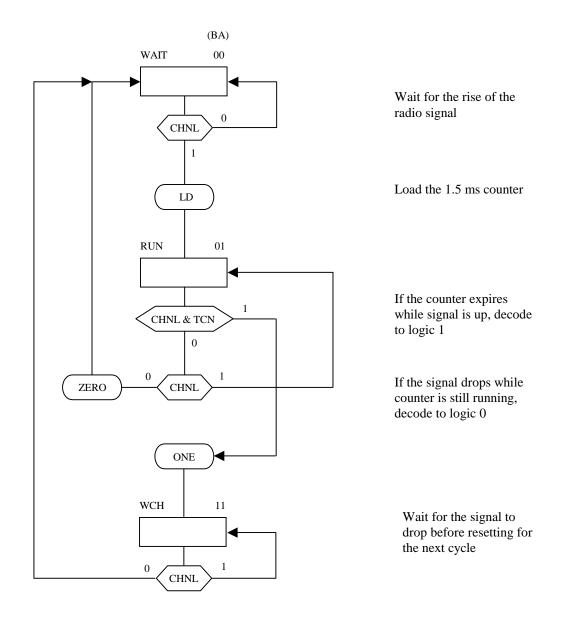

### **9.2.2** Control

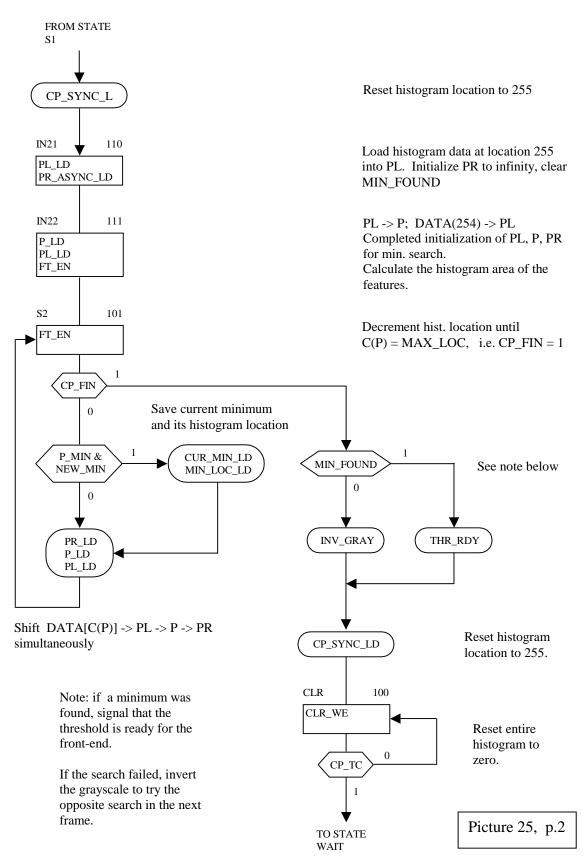

Control ASM is implemented in the Abel code component HIST\_ASM, shown in Picture 25 (two pages). The algorithm is by its nature sequential, and can be roughly divided into these six steps: initialize the address and the comp registers, search for the maximum, reinitialize, search for the minimum, notify front end or invert the grayscale, clear the histogram. Individual states and logic are explained in the ASM chart.

# **9.2.3** Signals

CP\_SYNC\_LD – synchronously load the value 255 into the address counter C(P).

CLR\_REG – synchronously clear registers PR, CUR\_MAX, MAX\_LOC.

PL\_LD, P\_LD, PR\_LD – enable loading of comp registers PL, P and PR.

CUR\_MAX\_LD, MAX\_LOC\_LD, CUR\_MIN\_LD, MIN\_LOC\_LD – enable loading of maximum/minimum registers.

PR\_ASYNC\_LD – asynchronously set registers PR and CUR\_MIN to "infinite" value.

THR\_RDY – notify the front end that the threshold is ready.

INV\_GRAY – set the grayscale inversion for the next frame.

CLR\_WE – enable writing zeros into the histogram.

NORM\_EN, FT\_EN – enable the accumulation of histogram and feature integrals.

FFR – feature integral is meaningful relative to the entire histogram area.

Picture 25: Control ASM for the histogram/threshold calculation, p.1

#### 10. DIGITAL ZOOM

It became very obvious during test flights that the human navigator and the vision steering system need two different perspectives on the ground scene. At altitudes of 200-300 ft, view through the wide-angle camera was adequate for general orientation, but the target was impractically small for the vision system to handle. Using a narrow-field (f=16 mm) lens, or equivalently, flying close to the ground, produced good target images if and when the target was ever located. The camera was fixed to the body of the plane, but even with an independently movable camera the navigator would have difficulties spotting areas of interest through the narrow field.

A camera with the zoom lens, or even two different cameras on the same gimbal, would solve this difficulty at the cost of additional mechanical equipment. However, since the vision system originally used only one sixth of the total image information (sampling every third line of the even field), there was room for electronic, instead of optical, zooming. Only the vision system sees the effect of the zoom, since the navigator currently receives no digitized image feedback.

The digital zoom, as implemented, is a 3X zoom. It amounts to using the full line density of the even field, sampling pixels at three times the "no zoom" rate. In order to maintain the same data volume, only the central one-ninth of the video image is actually digitized and passed to the vision system. A 6X zoom could be implemented by using the lines in the odd field also, but some care would have to be exercised regarding the end-of-field communication between processes.

## **10.1** Zoom implementation on the FPGA

The zoom has been implemented on the front-end FPGA, as part of the overall digitizing circuit. The zoom level is passed to the FPGA as a run-time parameter, and a selection is made between two sets of five constants. These five constants define the resolution and framing of the image.

In order to cope with high sampling frequency, the FPGA's clock rate is set to 33.3 MHz, and the pixel read/write cycle was made as short and pipelined as feasible (see description in Section 12). Picture 26 shows the zoom's geometry and the signals involved. Refer back to Section 7, Formatting the image scan, for details (p. 33).

Pictures 27 and 28 give an overview of the formatting, modified by the zoom. Picture 27 shows the sampling clock active in the central one-third of the lines of the even field. Greater magnification shows the sampling clock also limited to the central one-third of one line, with the black reference sample following the horizontal sync (Picture 28). The non-zero data signal (DR) is due to a dark object in the camera's field of vision.

When the zoom is engaged, rotations of the camera produce larger displacements in the image. Therefore, the procedure that calculates servo duty cycles must also take the zoom into account and turn the camera by smaller angles (see the program module Servo.s).

Picture 26: Formatting and zoom

Picture 27: Vertical formatting (zoom)

Picture 28: Horizontal formatting (zoom)

#### 11. ROUND ROBIN PROCEDURE FOR DATA SHARING

Presence of two processes (motion detection and feature recognition), running on separate processors, makes heavy demands on the memory containing the image data. In this system, access conflicts and bus logjams are avoided by using a dual-port SRAM chip and a round-robin data access procedure.

The RAM chip used is CY7C007AV,<sup>7</sup> an asynchronous 32K x 8 part by Cypress Semiconductor. It has two address/data ports, which can read simultaneously from the same memory location. The part arbitrates read/write access conflicts in hardware, although that feature is not used here. The chip also has a bank of hardware semaphores, with their own chip-select signals and arbitration logic. This feature was essential in implementing the round robin procedure.<sup>8</sup>

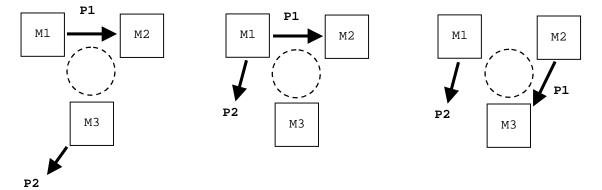

In this scheme, the motion detection (process P1) reads from one memory area, say M1, and writes into another (M2). It swaps these areas on each new video frame.

Feature recognition (P2) takes a few frames' time to complete one calculation. When P2 needs an update, it reads the P1's read frame, say M1 (P2 never writes). On the next video frame, P1 reads M2 and writes to M3, then swaps M2 and M3 until P2 claims whichever of these is P1's read frame at the moment (see Picture 29).

Picture 29: Round robin

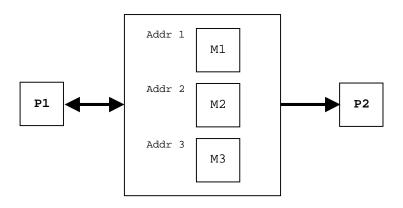

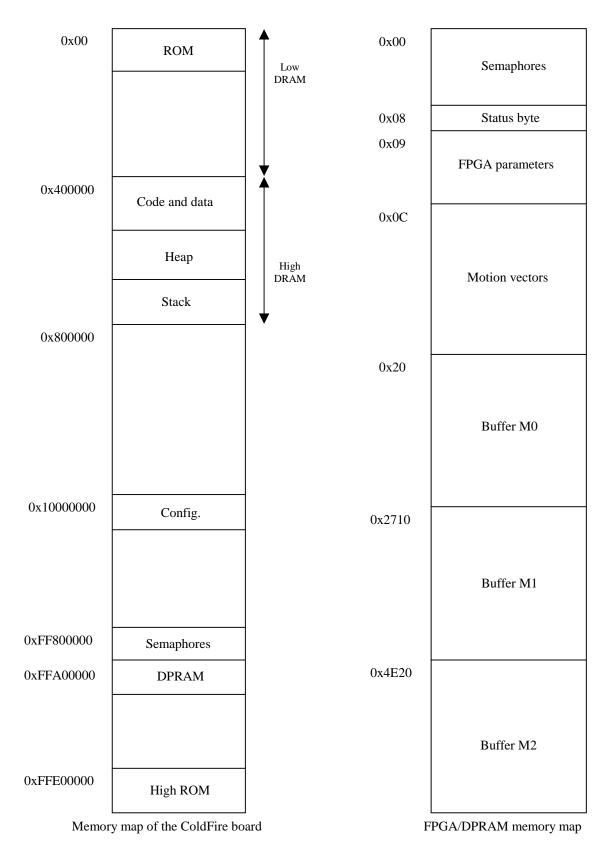

Picture 30: DPRAM's memory buffers

Buffers M1-M3 are implemented as distinct memory areas on the dual-port memory chip, and waiting is eliminated completely. P2 can start reading the P1's read frame through its own bus, and the round-robin motion is performed by switching the starting addresses of M1-M3 (see Picture 30). Read/write conflicts cannot occur on buffer access, only double reads, which are permitted by the DPRAM.

At any moment, each buffer is assigned to one of these three states: P1 writes, P1 reads, P2 reads; any buffer can be in any of them, and no two buffers are ever the same. The record of the current state is maintained in a dedicated location, the status byte, which is updated by P1 and P2 on every turn of the round robin.

Since P1 and P2 are mutually asynchronous, genuine access conflicts will occur on the status byte. These are avoided by protecting the status byte with the semaphore: only one port can hold the semaphore (this is arbitrated by the memory chip), and that port updates the status before releasing the semaphore. The other process stays in a polling loop until access is granted, but the duration of the busy wait is no more than a one-byte I/O operation, which is insignificant on either processor.

# 11.1 Status byte

The status byte, at the DPRAM address 0x08, contains three two-bit fields corresponding to the buffer states P1W, P1R and P2R, and the value in each field is the number of the buffer assigned to that state.

| 0x08 0 | 0 | P2R | P1R | P1W |

|--------|---|-----|-----|-----|

|--------|---|-----|-----|-----|

Maintenance of the status byte is very simple. On reset, its value is set to 0b00100100 (0x24), which means that:

- buffer zero is P1's write buffer

- buffer one is P1's read buffer

- buffer two is P2's read buffer

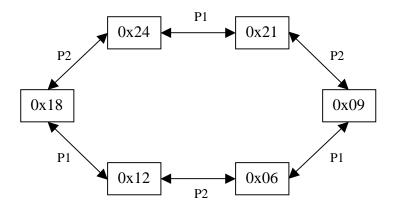

Process 1 swaps the contents of fields P1W and P1R (interchanges its working buffers). Process 2 swaps the contents of fields P1R and P2R (releases the buffer it just read and takes up the reading buffer of the Process 1). Between updates, each process maintains a private copy of the status information; otherwise, its working buffer(s) could change in mid-cycle, with disagreeable results. Picture 31 shows the allowed swaps of the status byte values.

Picture 31: Status byte values

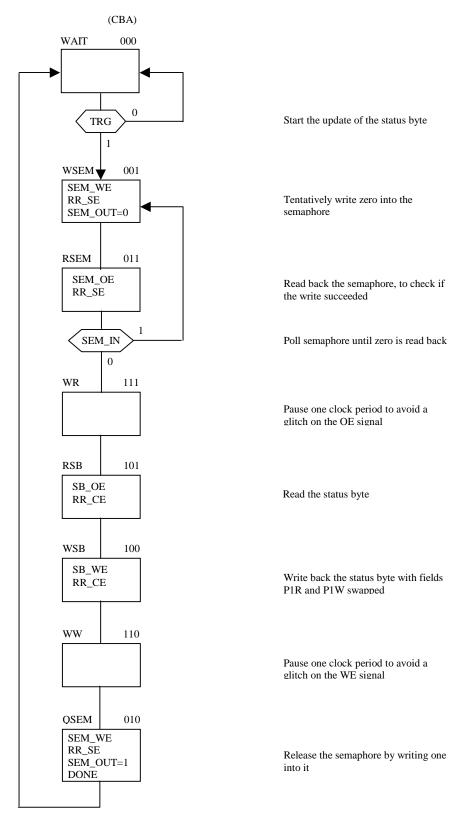

#### 11.2 Round Robin on the front-end FPGA

The procedure by which the two processes share buffers of image data in the DPRAM has already been described earlier. This section deals with the implementation of the round robin on the FPGA side, as the component ROUND\_ROBIN.

The private copy of the status byte resides in the register SBYTE\_REG, which is read from and written to the DPRAM address 0x08. Notice the peculiar ordering of input bus leads, which accomplishes the swapping of fields P1R and P1W.

Current addresses for the three image buffers reside in three counters driven by the LATE\_CLK (see schematic RR\_ADDRESS). Fields P1R and P1W are used to operate the multiplexer which selects the current buffer for read or write operations.

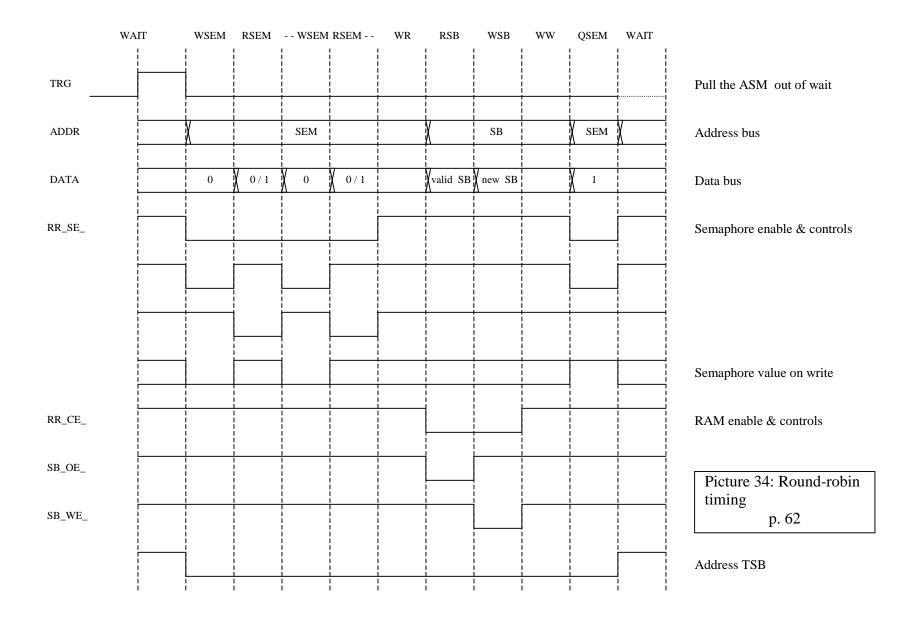

The ASM (see picture 33) is straightforward: it polls the semaphore for access, reads and writes the status byte, then releases the semaphore. Picture 34 shows the timing diagram.

SEM\_IN – read value of the semaphore.

SEM\_OUT – written value of the semaphore.

RR\_SE – semaphore enable (the semaphore's chip select).

SEM\_WE, SEM\_OE, SEM\_D\_TSB – control signals for the semaphore I/O.

RR\_CE – chip enable for the regular RAM area.

SB\_WE, SB\_OE - control signals for the RAM I/O.

STAT\_A\_TSB – address TSB control for the entire round robin sequence.

Picture 32: Semaphore-protected update of the status byte

Picture 33: Round-robin ASM

### 11.3 Round Robin on the MCF5307 processor

Implementation of the round robin procedure in code is straightforward: the flowchart is almost identical to the ASM chart in Picture 33. The procedure is invoked once in each pass of the feature recognition loop (see module main.c). It polls the semaphore for access and reads the status byte when the access is granted; swaps the fields P1R and P2R, updates the status byte and releases the semaphore. The new P2R (in the local copy of the status byte!) is used to select the starting address of the read buffer, and that address is made available to the vision code in the global variable IMAGE\_FRAME.

The subroutine round\_robin is contained in the program module RoundRobin.s, along with the subroutine config\_cs, which configures the left port (ColdFire side) of the DPRAM.

Note on the DPRAM addresses on MCF5307: The hardware is configured so that the ColdFire processor uses its chip select 4 for the semaphore bank of the DPRAM, and the chip select 5 for the regular storage area. ColdFire chip selects are assigned blocks of address space 2 MB in size; consequently, the base addresses for the semaphores and the regular RAM become 0xFF800000 and 0xFFA00000 respectively, even though they are contiguous in the DPRAM's address space (see Picture 48 on p. 98). ColdFire generates the proper address in the lower 15 bits, and the high bits serve only to activate the right chip select.

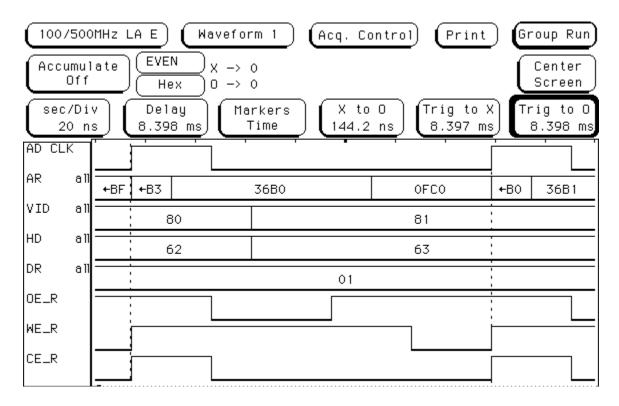

## 12. THE PIXEL READ/WRITE CYCLE

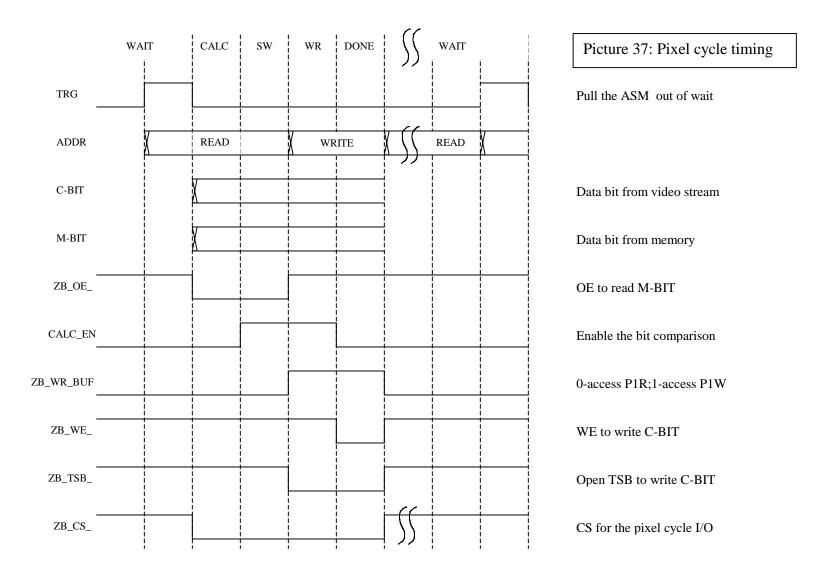

The pixel read/write cycle is central to the early vision processing: it stores the digitized B/W image and performs the motion detector's frame comparison. This section describes the cycle suitable for the 33.3 MHz system clock and the 5.4 MHz pixel sampling rate.

Events within the cycle are sequenced by the state machine PIXEL\_CYCLE, which is clocked by the system clock and runs one full sequence per period of the sampling clock.

The pixel cycle accesses two memory buffers, P1R and P1W; corresponding addresses of the pixel in these two buffers are determined by the round robin algorithm. Pixel calculation is triggered by the delayed sampling clock, LATE\_CLK, which also increments the buffer addresses.

The pixel's read address is calculated during the high time of the sampling clock, and the value is stable on the signal M\_BIT one clock period later; this is the pixel's value from the previous frame. The thresholded signal, C\_BIT, becomes available around the same time. Both bits are presented to the comparator/accumulator (see Section 13.3, the description of the FPGA design, p.70, for details) and the incremented value of the motion vector is clocked in one period later.

The address is now switched to the pixel's write address, and on the rising edge of WE, one clock after the address switch, the new pixel value is written to the write buffer. The

entire read/write cycle takes five clock cycles: at 33.3 MHz, this is sufficiently fast to complete all pixel processing at the sampling rate.

In addition, there are RAM-controlling signals in the cycle: output enable, write enable and the three-state output buffer on the zero bit of the data line. All of these are active low. Picture 37 shows the timing diagram of the read/write cycle, one column per state.

Picture 35 shows the read/write cycle driven by the 33.3 MHz clock, and running at the full sampling rate of the 3X zoom.

Picture 35: Pixel cycle

Picture 36: PIXEL\_CYCLE ASM

#### 13. FRAME COMPARISON AND THE MOTION VECTOR

# 13.1 Methodology

Motion detection in this system is limited to linear displacements of the entire scene, since we are interested only in detecting changes due to the movements of the plane (egomotion). Drift detection would perhaps be a more accurate term.

Formula used to calculate the motion vector is as follows:

$$\Delta = \frac{\sum x_i (\Delta pix)_i}{\sum pix_j}$$

This is essentially the formula for the dipole moment of the displacement, with the previous frame's pixels counting as the negative charge, and the current frame as positive. Summations are over the entire image, pix is the pixel value (zero or one),  $\Delta pix$  is the difference between consecutive frames, and  $x_i$  is the i-th pixel's position. The normalization constant in the denominator is simply the number of black pixels in the image.

Motion detection in the vision of insects with composite eyes utilizes the principle of consecutive activation/deactivation of receptors; direction of motion is determined by the pattern of neural wiring between adjacent receptors (eyelets in the composite eye). Our detector has no pixel adjacency information, and cannot detect local motion within the image. Instead, it obtains an integrated value of spatial distances between activated/deactivated pixels. For simple drift motion, this is an adequate motion vector,

with the caveat that the detector is sensitive to appearance of new objects in the periphery, which it interprets as motion.

# 13.2 Computation

Pixels are processed in real time, and each pixel cycle contains the following steps:

- corresponding pixel from previous frame is read from the DPRAM buffer P1R;

- current and previous pixel are presented to two comparators, which calculate the components of the motion vector;

- current pixel is stored in the DPRAM buffer P1W.

Each b/w pixel is stored in the zero-th bit of a byte, which makes addressing simpler and faster. Higher bits of these bytes are not used.

## 13.3 Design components

*line-in-frame counter* - counts scanned video lines within one frame. Used as the vertical (Y) coordinate of the current pixel.

*pixel-in-line counter* - counts the sampling clock (LATE\_CLK), starting at the beginning of each video line. Used as the horizontal (X) coordinate of the current pixel.

*pixel-in-frame counter* - counts the sampling clock (LATE\_CLK), starting at the beginning of a frame. It resets to the starting address of the frame in the SRAM, and its value is used as the address of the SRAM byte that contains the current pixel.

COMP\_ACCUM - comparator/accumulator; this component adds/subtracts the value on the input bus NUM[31:0] to/from the current value in its internal register. The current value is always available on the output bus SUM[31:0]. The sign of the operation depends on the values of CBIT and MEM, as follows:

| CBIT | MEM | operation |

|------|-----|-----------|

| 0    | 0   | none      |

| 1    | 0   | add       |

0 1 sub

1 1 none

This operation is designed to capture the differences in pixels of adjacent frames. It is enabled by the EN signal. ASYNC\_CTRL resets the register value to zero asynchronously, and no operations take place while ASYNC\_CTRL is high.

black pixel counter - counts the sampling clock (LATE\_CLK), starting at the beginning of a frame, only if C\_BIT is high on the rising edge of the clock. Count of black pixels in one frame.

# 13.4 Signals

C\_BIT – single-bit output of the digitizing/thresholding circuit ANALOG\_IN. This is the current pixel of the current frame.

M\_BIT - current pixel of the previous frame, retrieved from DPRAM and compared with the C\_BIT to detect motion.

CALC\_EN – enable signal for the comparison; output of the PIXEL\_CYCLE sequencing ASM.

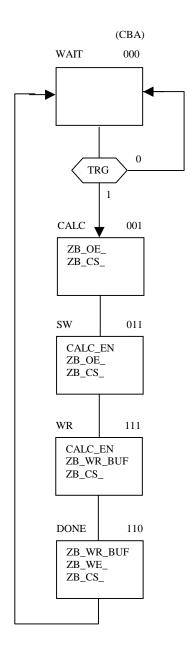

# 14. WRITING THE MOTION VECTOR TO DPRAM

At the beginning of the odd field, vector components and the normalization constant are written in DPRAM, at the address 0x0C, as three longwords in the big endian order.

Component VECT\_OUT handles that procedure.

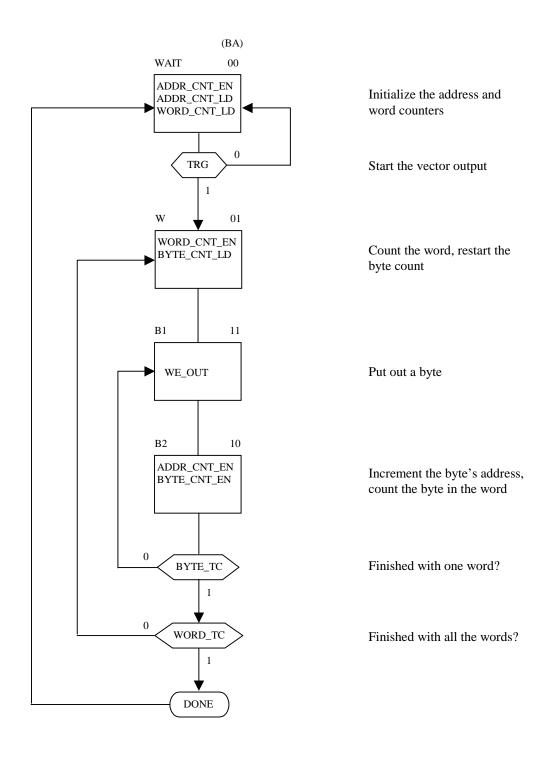

VECT\_OUT has an address counter, a word counter and a byte-in-word counter. The latter two counters operate the multiplexers which select the proper byte for output, and the whole procedure consists of a straightforward double loop, corresponding to three words and four bytes per word. The ASM chart is shown in Picture 39.

TRG – the trigger signal.

...\_CNT\_EN, ...\_CNT\_LD – control signals for the counters

WE\_OUT, TSB - DPRAM control signals

DONE – ending signal; signal to the next stage to proceed.

Picture 38: Vector output

Picture 39: VECT\_OUT ASM

#### 15. PARAMETERS OF THE FRONT-END FPGA

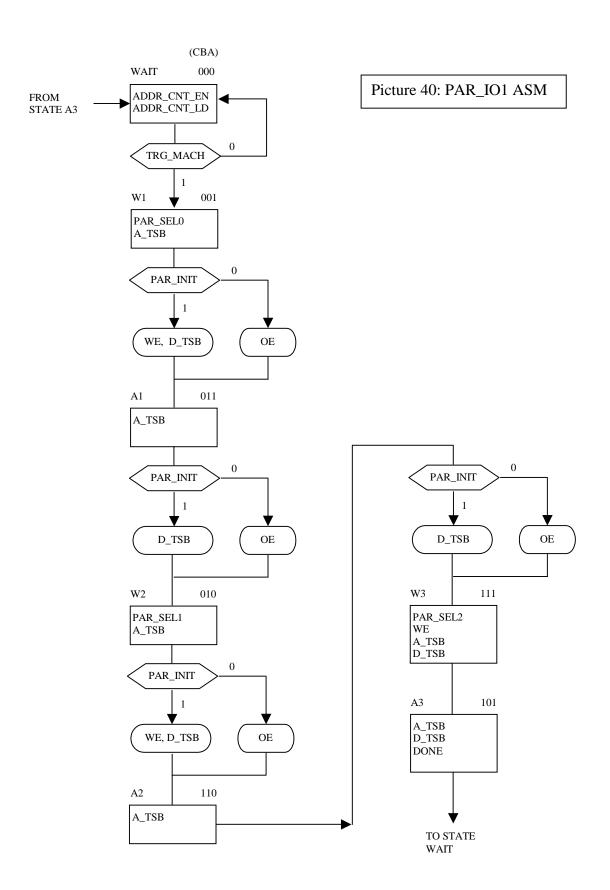

The component PAR\_IO1 handles the parameter logistic. Currently, there are three byte-size parameters allocated to the front-end FPGA, starting at the DPRAM address 0x09:

- b/w threshold, (0-255)

- one byte of bitwise parameters:

- o bit 0 b/w inversion; zero stands for dark features, one for bright features

- o bit 1 zoom level: zero for no zoom, one for 3X zoom

- mailbox, written to DPRAM on each frame:

- o bit 0 zoom level indicator: zero for no zoom, one for 3X zoom

Parameters can be added as needed, by a fairly straightforward extension of this component.

Default values of the parameters are contained in the circuit, as byte-size constants. On the first high TRG after power-up, that is on the first odd field, default parameters are written to DPRAM at consecutive addresses. On subsequent TRGs, each parameter's address is presented on the bus ADDR\_OUT, and the corresponding parameter selection signal goes high, for the duration of two clocks. This allows the current parameter values to be read from DPRAM and latched into parameter registers in the circuit. The mailbox parameter is written to DPRAM on each frame, to be read by the microprocessor.

The ColdFire program updates the parameters in the DPRAM during the IRQ5 handler, and reads the mailbox. This mechanism allows for changes in the parameters to be made

at run time, e.g. by operator commands, as well as for the FPGA to send signals to the ColdFire. Currently, the mailbox is used to notify the ColdFire when the zoom command has been radioed to the front-end FPGA.

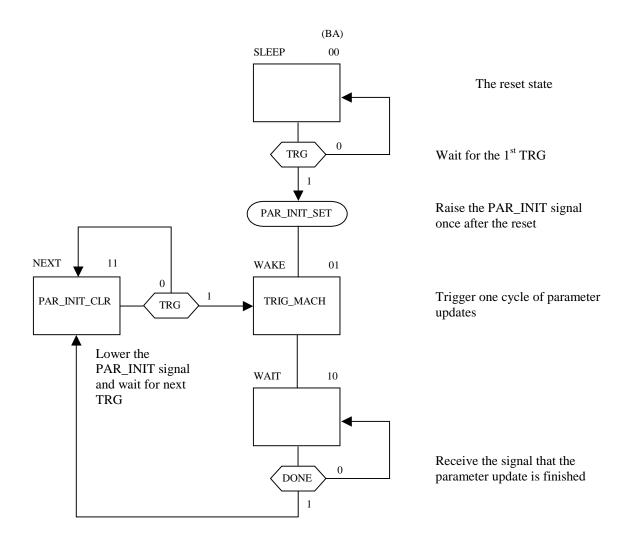

Sequencer ASM for PAR\_IO1 is shown in Picture 40. Its subcomponent, INIT\_BOX, raises PAR\_INIT once after the power-up, and its ASM is shown in Picture 41.

TRG – the trigger signal; high once per frame, at the start of odd field

TRG\_MACH – derivative trigger, produced by the initialization component INIT\_BOX.

ADDR\_CNT\_EN, ADDR\_CNT\_LD – signals that control the address counter

PAR\_INIT – high on first occurrence of the TRG; passes the default parameter values onto the PAR\_IO bus.

A\_TSB, D\_TSB, OE\_OUT, WE\_OUT – RAM control signals involved in parameter I/O to and from the DPRAM.

PAR\_SEL0, PAR\_SEL1, PAR\_SEL2 – parameter selectors; enable latching of the corresponding parameter in the appropriate data register in the circuit.

PAR\_IO – data bus which carries the parameters.

Picture 41: INIT\_BOX ASM

Picture 42: FPGA parameters

# 16. THE IRQ5/PARALLEL PORT COMPLEX

A tightly coupled hardware/software subsystem, centered around the Interrupt 5 and the parallel port of the MCF5307, coordinates the back-end data flow in the vision system. Here we describe that subsystem.

## 16.1 IRQ5 handler

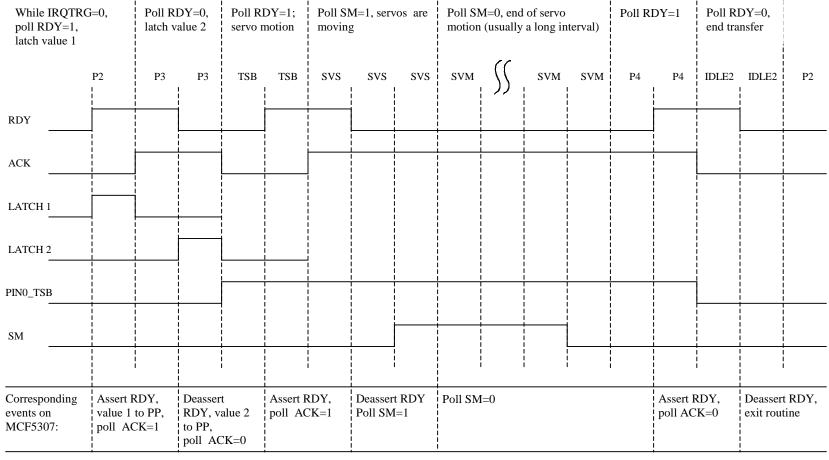

Early in the odd field, after the motion vector has been written to the DPRAM, back-end FPGA generates an IRQ5, as a hardware signal to the MCF5307. When the processor enters the IRQ5 handler, the interrupt is acknowledged by a handshake on the parallel port, via two signals, ACK and RDY (bits 14 and 15).

The motion vector is read from DPRAM (it was written before the IRQ5, so there is no access conflict), and it is normalized by dividing by the black pixel count. This operation is performed here and not in the front-end FPGA, where the vector is generated, because of long integer divisions.

Subject to some size restrictions, the vector is translated into increments in the servo cycle's pulse widths, and these increments are used to update the current pulse widths.

Notice that the desired position of the camera is always known to the vision system (in the form of calculated pulse widths), but that the actual position may not be known in real time.

# 16.2 Duty-cycle generator

The generator of the pulse modulated servo signals resides on the back-end FPGA. It receives the pulse widths from the IRQ5 handler, and produces the corresponding waveforms. Pulse widths are passed as 14-bit numbers on the parallel port, in a protocol synchronized by the ACK/RDY signals.

## 16.3 Servo motion feedback

When the pulse width changes, the servos start moving into the new position. The servo circuit, built around a PIC16F877 microprocessor, detects the pulse change and begins to monitor the angle of the servo shaft, as an analog signal. It asserts the servo-move signal, which remains high until the servos have stopped.

In this fashion, the instantaneous information about the camera position is decoupled from the vision system. The vision merely issues the desired position, and receives confirmation when that position is reached.

While the servo motors are moving to their new position, the IRQ5 is not being generated, since the motion detector would counteract the displacement motion, leading to unsteady movement of the camera.

## 16.4 Displacement vector

When it is not communicating with the IRQ5 handler, the duty-cycle generator waits for the displacement vector transfer, initiated by the MCF5307. The displacement vector is being calculated by the Process 2, and when ready, it is transferred to the back-end FPGA in the same way as the motion vector.

In this transfer sequence, however, the servo-motion signal (the response to the new displacement vector) is passed back to the MCF5307, forcing the Process 2 into a busy wait until the servos have stopped moving. This might appear wasteful at first, but it is easy to see that Process 2 really must pause during the servo motion. The snapshot for feature recognition must not be taken until the camera has moved to the new location. Otherwise, the change in the image would not be registered, and the next cycle of feature recognition would end up working with stale data.

## 16.5 Saccadic blanking

On the face of it, this suppression of image sampling during camera motion resembles the phenomenon of saccadic blanking in human/animal vision.<sup>12</sup> It is well known that the sensitivity of the optic nerve is suppressed while a saccade (a rapid eye movement) is in progress, and it is plausible that the purpose of this suppression is to prevent visual confusion in biological systems as well.

Interestingly, there is some question whether the suppression of the optic nerve signal is triggered by the blurring of retinal image or by a signal from tension sensors in the eye muscles.<sup>13</sup> In a robotic system it is much easier to detect servo motion than image blur, and the choice of mechanism is obvious.

# 16.6 Description of the IRQ/PP circuit on the back-end FPGA

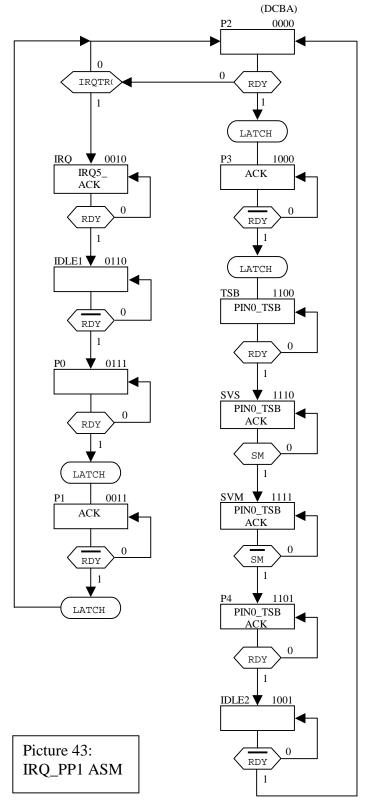

The circuit design is contained in the schematic DUTY\_CYC\_PP. Control of the process is carried out by the ASM component IRQ\_PP1, described in the previous section (see also ASM chart, Picture 43, and timing diagrams, Pictures 44 and 45).

The data path leads from the parallel port to two 14-bit registers, which hold the current pulse-width values. These values are in turn available to the square-pulse generators.

The pulse generator component, CYCLE\_GEN, contains a fixed-value counter, which measures the 20 ms period of the servo's duty cycle, and a loadable counter, which measures the current pulse width. A simple two-state ASM switches between high and low signal levels.

The servo-move signal passes through the component DIP\_FILTER which eliminates the short (less than a CLK cycle) dips in the signal (noise).

ACK, RDY – handshake signals on the parallel port:

ACK - pin 14, output

RDY - pin 15, input

IRQTRG – signal from the front-end FPGA to start the IRQ5 communication at the start of odd field (see Picture 18).

IRQ – hardware request for Interrupt 5 on ColdFire.

SERVO\_MOVE – the cleaned-up servo motion signal; also sent out to pin 0 on the parallel port.

PINO\_TSB – signal which reverses the sense of pin 0: output when high, input when low.

Pins 1-13 are all input pins

LATCH1, LATCH2 – register-enable signals to capture the pulse width values.

PWM1, PWM2 – generated servo duty waveforms.

Comm. with

Acknowledge

terminate IRQ5

widths into data

handler and

Latch pulse

registers.

handler:

signal.

Comm with Proc.2:

Latch pulse widths into data registers.

Poll the servo motion signal until it goes high, then low again. Idle during that time.

| While RDY=0, poll IRQTRG=1; start |    | Poll for RDY = 1; C.F. acknowledges IRQ5 |                    | 1 1  |                  |                  |               |                  | Poll RDY=0, latch value 2   |             | Picture 4-<br>Commun<br>IRQ5 har | ication with the |                                            |                              |

|-----------------------------------|----|------------------------------------------|--------------------|------|------------------|------------------|---------------|------------------|-----------------------------|-------------|----------------------------------|------------------|--------------------------------------------|------------------------------|

|                                   | P2 | P2                                       | IRQ                | IRQ  | IRQ              | IDLE1            | IDLE1         | P0               | P0                          | P1          | P1                               | P2               | <u>                                   </u> |                              |

| IRQTRG -                          |    |                                          | <br>               |      |                  | <br>             |               | <br>             |                             | <br>        |                                  |                  | once per fra                               | art the IRQ5 exchange, ame   |

| IRQ5                              |    | <br>                                     |                    | <br> | <br>             |                  | <br>          | !<br>!<br>!      |                             | !<br>!<br>! |                                  | !<br>!<br>!<br>! | handler rou                                |                              |

| RDY                               |    | <br>                                     | <br>               | <br> |                  | <br>             |               | <br>             |                             | <br>        |                                  | <br>             |                                            |                              |